Fabric DDR Subsystem

Microsemi ProprietaryUG0446 User Guide Revision 7.0

144

Note:

AHBx indicates AHB0 or AHB1.

4.5.2.3

APB Slave

The following table describes the FDDR APB slave interface signals. For APB protocol details, refer to

AMBA APB v3.0 protocol specification

4.6

Initialization

After power-up, the FDDR needs to have all of the configuration registers written to establish the

operating modes of the blocks. When using the

System Builder

design flow through Libero SoC, this is

all handled for the user through the use of the

System Builder

module. All of the configuration register

values are selected by the user and stored in a special portion of the eNVM. Before the FDDR

subsystem is active, it goes through an initialization phase and this process starts with a reset sequence.

For DDR3 memories, the initialization phase also includes ZQ calibration and DRAM training.

4.6.1

Reset Sequence

The following illustration shows the required reset sequence for FDDR subsystem from the power-on-

reset stage. The CORE_RESET_N signal of the FDDR subsystem must be asserted after

MSS_RESET_N_M2F/ HPMS_RESET_N_M2F and FDDR FPLL lock go High and APB register

configuration is complete. Assertion of CORE_RESET_N signifies the end of the reset sequence. The

DDR controller performs external DRAM memory reset and initialization as per the JEDEC specification,

including reset, refresh, and mode registers.

AHBx_S_HTRANS[1:0]

Input

Indicates AHB transfer type from Fabric master.

00: IDLE

01: BUSY

10: NONSEQUENTIAL

11: SEQUENTIAL

AHBx_S_HMASTLOCK

Input

High

Indicates AHB master lock signal from Fabric master.

AHBx_S_HWRITE

Input

High

Indicates AHB write control signal from Fabric master.

AHBx_S_HREADY

Input

High

Indicates that a transfer has finished on the bus. Fabric master

can drive this signal LOW to extend a transfer.

AHBx_S_HWDATA[31:0] Input

Indicates AHB write data from Fabric master.

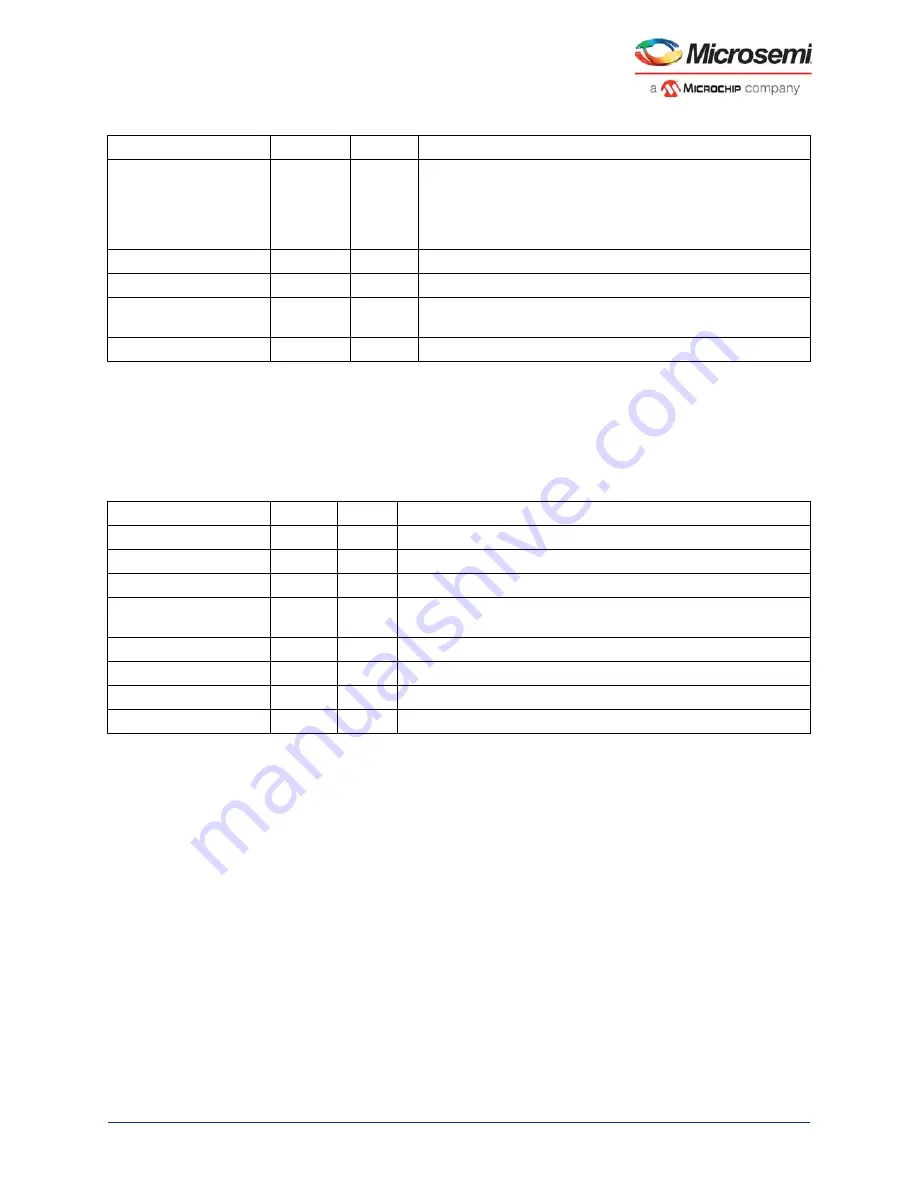

Table 131 •

FDDR APB Slave Interface Signals

Signal Name

Direction Polarity Description

APB_S_PREADY

Output

High

Indicates APB Ready signal to Fabric master.

APB_S_PSLVERR

Output

High

Indicates error condition on an APB transfer to Fabric master.

APB_S_PRDATA[15:0]

Output

Indicates APB read data to Fabric master.

APB_S_PENABLE

Input

High

Indicates APB enable from Fabric master. The enable signal is used

to indicate the second cycle of an APB transfer.

APB_S_PSEL

Input

High

Indicates APB slave select signal from Fabric master

APB_S_PWRITE

Input

High

Indicates APB write control signal form Fabric master

APB_S_PADDR[10:2]

Input

Indicates APB address initiated by Fabric master.

APB_S_PWDATA[15:0]

Input

Indicates APB write data from Fabric master.

Table 130 •

FDDR AHB Slave Interface Signals

(continued)

Signal Name

Direction

Polarity

Description