DDR Bridge

Microsemi Proprietary UG0446 User Guide Revision 7.0

207

5

DDR Bridge

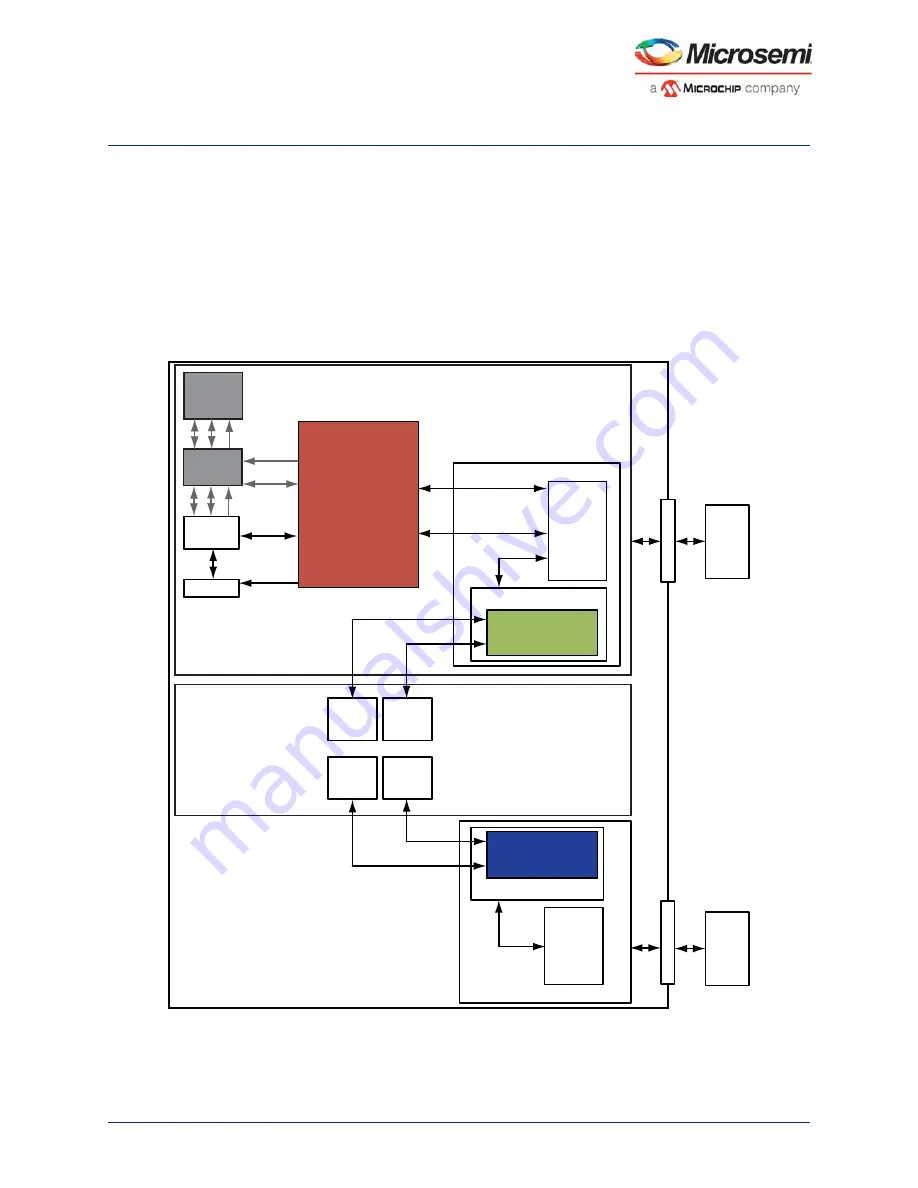

The DDR bridge facilitates multiple AHB bus masters to access a single AXI slave and optimizes read

and write operations from multiple AHB masters to a single external DDR memory. The SmartFusion2

and IGLOO2 devices have three instances of the DDR bridge, one each for the MSS/HPMS, FDDR, and

MDDR subsystems, as shown in the following image. The DDR bridge implemented in the MSS/HPMS

(shown in red) provides an interface between AHB masters within the MSS/HPMS for accessing DDR

memory. The DDR bridge implemented in the MDDR subsystem (shown in green) provides an interface

between the user implemented AHB masters in the FPGA fabric for accessing DDR memory. Similarly,

the DDR bridge in the FDDR (shown in blue) subsystem facilitates fabric masters to access DDR

memory.

Figure 127 •

DDR Bridges in the SmartFusion2/IGLOO2 FPGA Device

The DDR bridge supports a single 64-bit AXI and up to four 32-bit AHB interfaces. For SmartFusion2 the

four MSS AHB masters are fixed, as shown in the following table. For Igloo2, the two HPMS AHB

MSS/HPMS

DDR Bridge

AHB Bus

Matrix

ARM

Cortex-M3

Processor

Cache

Controller

HPDMA

DDR

Bridge

DDR_FIC

MDDR Subsystem

MSS/HPMS

DDR

Memory

DDR

Memory

DDR

Bridge

DDR_FIC

FDDR Subsystem

Fabric

AHB

Master 0

AHB

Master 1

AHB

Master 1

AHB

Master 0

AXI

Transaction

Controller

AXI

Transaction

Controller

32-bit AHB

32-bit AHB

128-bit AHB

32-bit AHB

32-bit AHB

64-bit AXI

64-bit AXI

64-bit AXI

32-bit AHB

32-bit AHB

32-bit AHB

SmartFusion2/IGLOO2

M

S

S

S

S

M

M

M

M

M

M

M

M

M

M

S

S

S

S

S

S

S

D

D

R

I

O

D

D

R

I

O

Note:

Grey blocks and arrows indicate the steps happen only in MSS. Rest are same in SmartFusion2 and IGLOO2.