MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

59

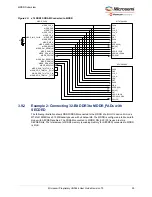

Figure 43 •

x16 DDR2 SDRAM Connected to MDDR

3.9.2

Example 2: Connecting 32-Bit DDR3 to MDDR_PADs with

SECDED

The following illustration shows DDR3 SDRAM connected to the MDDR of a IGLOO2 device. Micron’s

MT41J512M8RA is a 512 MB density device with x8 data width. The MDDR is configured in full bus width

mode with SECDED enabled. The SDRAM connected to MDDR_DQ_ECC[3:0] is used to store

SECDED bits. The total amount of DDR3 memory (excluding memory for SECDED) connected to MDDR

is 2 GB.

CASN

CKE

CLK_P

CLK_N

CSN

ODT

RASN

WEN

ADDR[12:0]

BA[2:0]

MT47H64M16

MDDR_CAS_N

MDDR_CKE

MDDR_CLK

MDDR_CLK_N

MDDR_CS_N

MDDR_ODT

MDDR_RAS_N

MDDR_WE_N

MDDR_ADDR[12:0]

MDDR_BA[2:0]

MDDR_DM_RDQS[1:0]

MDDR_DQS[1:0]

MDDR_DQS_N[1:0]

MDDR_DQ[15:0]

DQ[15:0]

UDQS#, LDQS#

UDQS, LDQS

DM

CASN

CKE

CLK_P

CLK_N

CSN

ODT

RASN

WEN

ADDR[12:0]

BA[2:0]

MT47H64M16

DQ[15:0]

UDQS#, LDQS#

UDQS, LDQS

DM

MDDR_DM_RDQS[3:2]

MDDR_DQS[3:2]

MDDR_DQS_N[3:2]

MDDR_DQ[31:16]

MDDR_PADS

MDDR_DQS_TMATCH_0_IN

MDDR_DQS_TMATCH_0_OUT

MDDR_DQS_TMATCH_1_IN

MDDR_DQS_TMATCH_1_OUT

MDDR_IMP_CALIB

R