MDDR Subsystem

Microsemi Proprietary UG0446 User Guide Revision 7.0

63

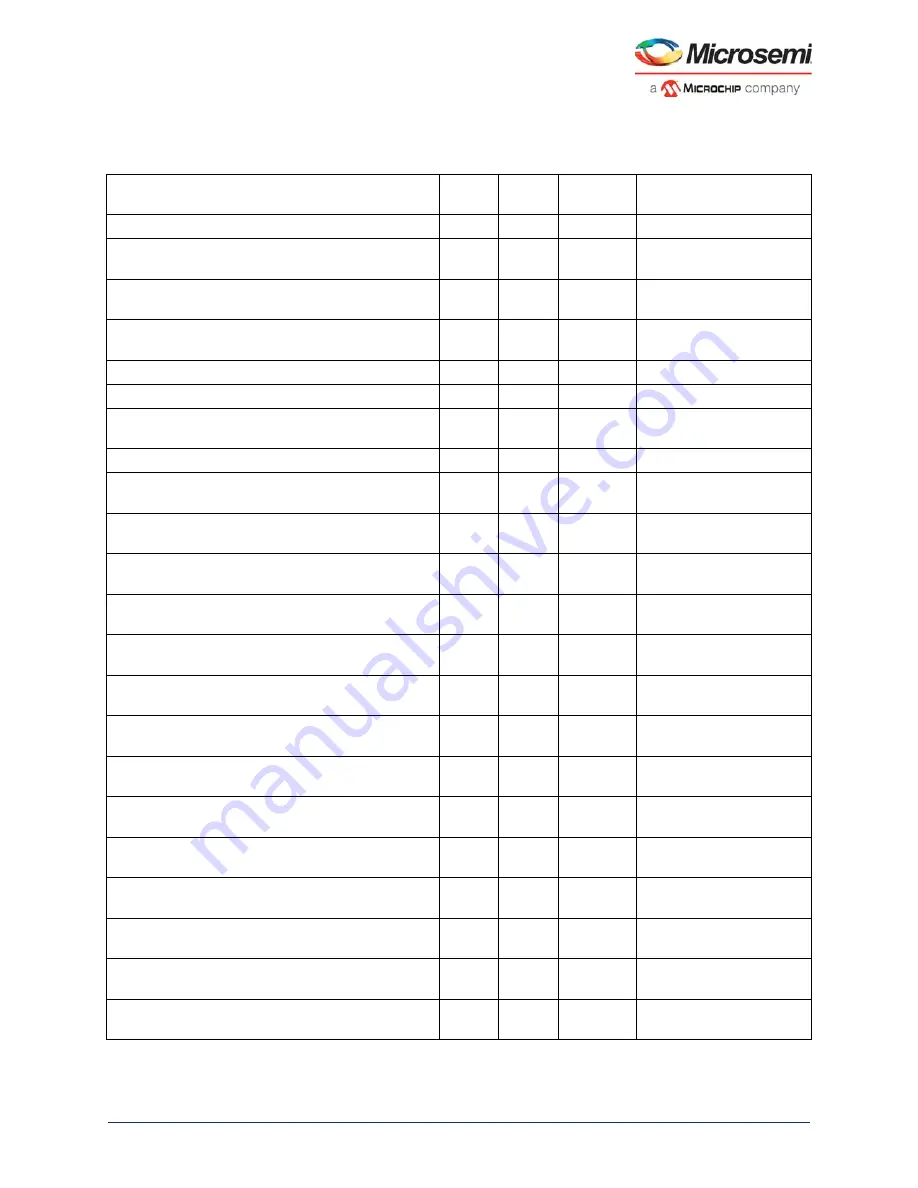

3.11.2

DDR Controller Configuration Register Summary

Table 28 •

DDR Controller Configuration Register

Register Name

Addres

s Offset

Registe

r Type

Reset

Source

Description

0×000

RW/RO PRESET_N DDRC Reset register

0×008

RW

PRESET_N DDRC Refresh Control

register

0×00C

RW

PRESET_N DDRC Refresh Control

register

0×010

RW

PRESET_N DDRC Power-Down Control

register

Reserved

0×014

-

-

-

0×018

RW

PRESET_N DDRC Mode register

0×01C

RW

PRESET_N DDRC Bank Address Map

register

Reserved

0×020

-

-

-

0×024

RW

PRESET_N DDRC Column Address

Map register

0×028

RW

PRESET_N DDRC Column Address

Map register

0×02C

RW

PRESET_N DDRC Row Address Map

register

0×030

RW

PRESET_N DDRC Row Address Map

register

0×034

RW

PRESET_N DDRC Initialization Control

register

0×038

RW

PRESET_N DDRC Initialization Control

register

0×03C

RW

PRESET_N DDRC Initialization Control

register

0×040

RW

PRESET_N DDRC MR Initialization

register

0×044

RW

PRESET_N DDRC EMR Initialization

register

0×048

RW

PRESET_N DDRC EMR2 Initialization

register

0×04C

RW

PRESET_N DDRC EMR3 Initialization

register

DDRC_DRAM_BANK_TIMING_PARAM_CR

0×050

RW

PRESET_N DDRC DRAM Bank Timing

Parameter register

0×054

RW

PRESET_N DDRC DRAM Write Latency

register

0×058

RW

PRESET_N DDRC DRAM Read-Write

Precharge Timing register