PIC16F716

DS41206A-page 18

Preliminary

2003 Microchip Technology Inc.

2.5

Indirect Addressing, INDF and

FSR Registers

The INDF register is not a physical register. Addressing

INDF actually addresses the register whose address is

contained in the FSR register (FSR is a pointer). This is

indirect addressing.

EXAMPLE 2-1:

INDIRECT ADDRESSING

• Register file 05 contains the value 10h

• Register file 06 contains the value 0Ah

• Load the value 05 into the FSR register

• A read of the INDF register will return the value of

10h

• Increment the value of the FSR register by one

(FSR = 06)

• A read of the INDR register now will return the

value of 0Ah.

Reading INDF itself indirectly (FSR =

0

) will produce

00h. Writing to the INDF register indirectly results in a

no-operation (although Status bits may be affected).

A simple program to clear RAM locations 20h – 2Fh

using indirect addressing is shown in Example 2-2.

EXAMPLE 2-2:

HOW TO CLEAR RAM

USING INDIRECT

ADDRESSING

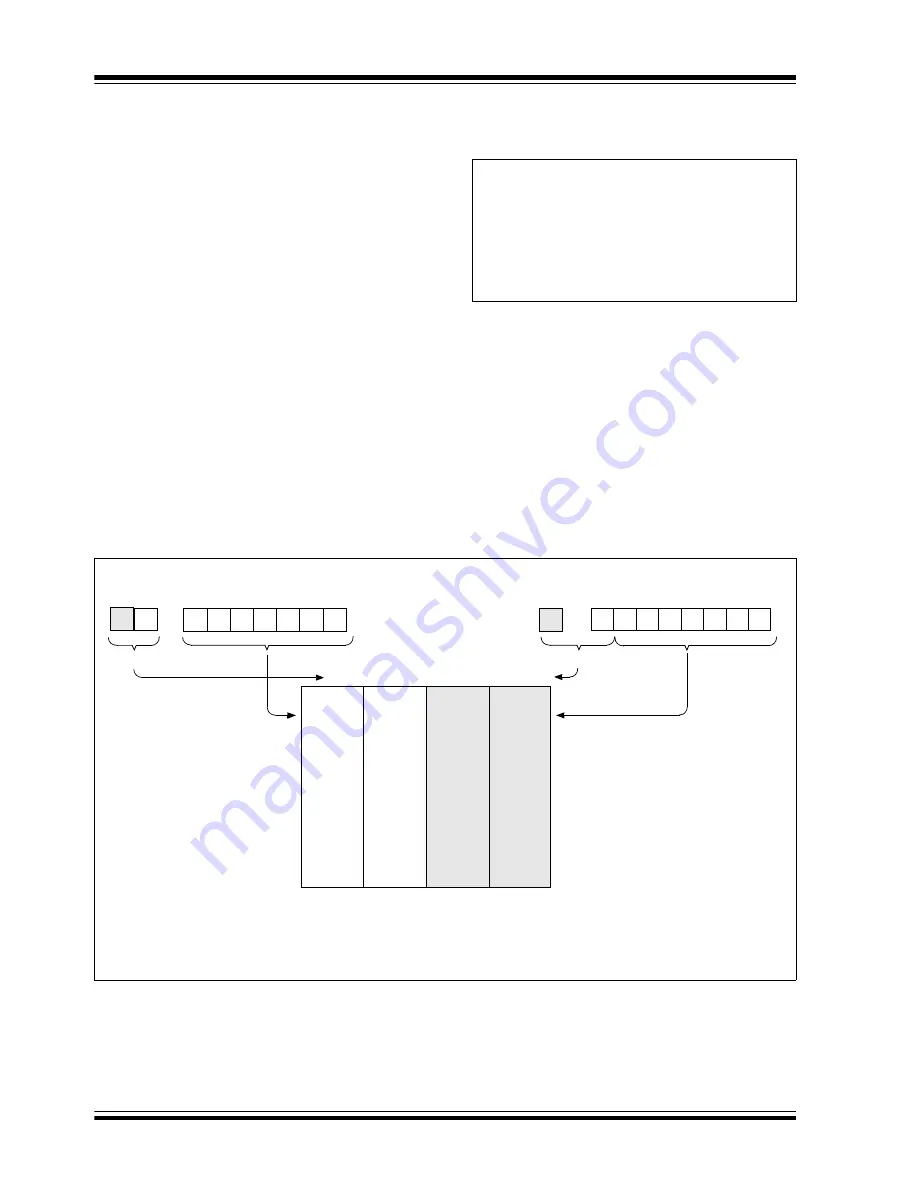

An effective 9-bit address is obtained by concatenating

the 8-bit FSR register and the IRP bit (STATUS<7>), as

shown in Figure 2-4. However, IRP is not used in the

PIC16F716.

FIGURE 2-4:

DIRECT/INDIRECT ADDRESSING

MOVLW

0x20

;initialize pointer

MOVWF

FSR

;to RAM

NEXT

CLRF

INDF

;clear RAM & FSR

INCF

FSR

;inc pointer

BTFSS

FSR,4

;all done?

GOTO

NEXT

;no, clear next

CONTINUE

:

;yes, continue

Note

1:

For register file map detail see Figure 2-2.

2:

Maintain clear for upward compatibility with future products.

3:

Not implemented.

Data

Memory

(1)

Indirect Addressing

Direct Addressing

bank select

location select

RP1: RP0

6

0

from opcode

IRP

FSR register

7

0

bank select

location select

00

01

10

11

Bank 0

Bank 1

Bank 2

Bank 3

FFh

80h

7Fh

00h

17Fh

100h

1FFh

180h

(3)

(3)

(2)

(2)

Summary of Contents for PIC16F716

Page 6: ...PIC16F716 DS41206A page 4 Preliminary 2003 Microchip Technology Inc NOTES...

Page 35: ......

Page 56: ......

Page 60: ......

Page 88: ......

Page 92: ...PIC16F716 DS41206A page 90 Preliminary 2003 Microchip Technology Inc NOTES...

Page 108: ...PIC16F716 DS41206A page 106 Preliminary 2003 Microchip Technology Inc NOTES...

Page 110: ...PIC16F716 DS41206A page 108 Preliminary 2003 Microchip Technology Inc NOTES...

Page 124: ...PIC16F716 DS41206A page 122 Preliminary 2003 Microchip Technology Inc NOTES...