PIC16F716

DS41206A-page 72

Preliminary

2003 Microchip Technology Inc.

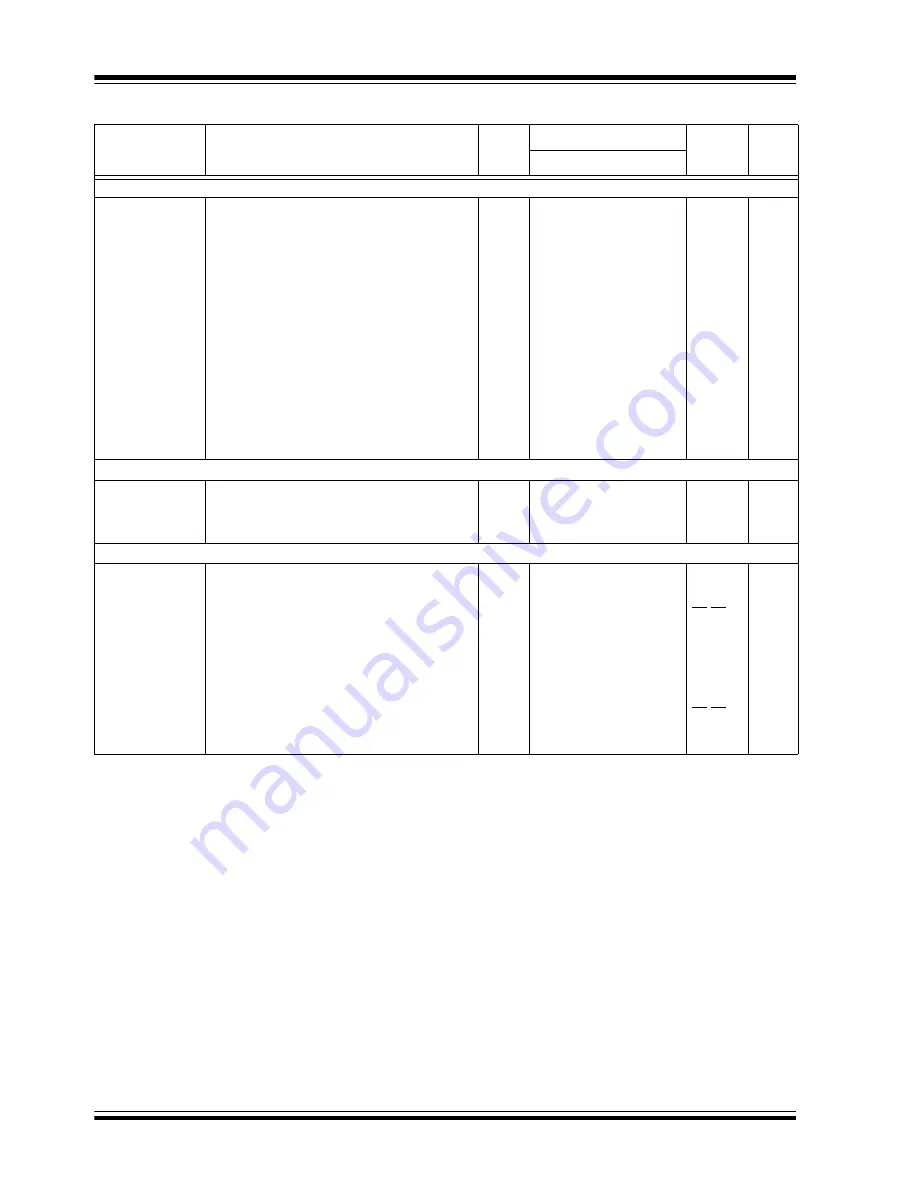

TABLE 10-2:

PIC16F716 INSTRUCTION SET

Mnemonic,

Operands

Description

Cycles

14-Bit Opcode

Status

Affected

Notes

MSb

LSb

BYTE-ORIENTED FILE REGISTER OPERATIONS

ADDWF

ANDWF

CLRF

CLRW

COMF

DECF

DECFSZ

INCF

INCFSZ

IORWF

MOVF

MOVWF

NOP

RLF

RRF

SUBWF

SWAPF

XORWF

f, d

f, d

f

—

f, d

f, d

f, d

f, d

f, d

f, d

f, d

f

—

f, d

f, d

f, d

f, d

f, d

Add W and f

AND W with f

Clear f

Clear W

Complement f

Decrement f

Decrement f, Skip if 0

Increment f

Increment f, Skip if 0

Inclusive OR W with f

Move f

Move W to f

No Operation

Rotate Left f through Carry

Rotate Right f through Carry

Subtract W from f

Swap nibbles in f

Exclusive OR W with f

1

1

1

1

1

1

1

(2)

1

1

(2)

1

1

1

1

1

1

1

1

1

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

00

0111

0101

0001

0001

1001

0011

1011

1010

1111

0100

1000

0000

0000

1101

1100

0010

1110

0110

dfff

dfff

lfff

0xxx

dfff

dfff

dfff

dfff

dfff

dfff

dfff

lfff

0xx0

dfff

dfff

dfff

dfff

dfff

ffff

ffff

ffff

xxxx

ffff

ffff

ffff

ffff

ffff

ffff

ffff

ffff

0000

ffff

ffff

ffff

ffff

ffff

C,DC,Z

Z

Z

Z

Z

Z

Z

Z

Z

C

C

C,DC,Z

Z

1,2

1,2

2

1,2

1,2

1,2,3

1,2

1,2,3

1,2

1,2

1,2

1,2

1,2

1,2

1,2

BIT-ORIENTED FILE REGISTER OPERATIONS

BCF

BSF

BTFSC

BTFSS

f, b

f, b

f, b

f, b

Bit Clear f

Bit Set f

Bit Test f, Skip if Clear

Bit Test f, Skip if Set

1

1

1

(2)

1

(2)

01

01

01

01

00bb

01bb

10bb

11bb

bfff

bfff

bfff

bfff

ffff

ffff

ffff

ffff

1,2

1,2

3

3

LITERAL AND CONTROL OPERATIONS

ADDLW

ANDLW

CALL

CLRWDT

GOTO

IORLW

MOVLW

RETFIE

RETLW

RETURN

SLEEP

SUBLW

XORLW

k

k

k

—

k

k

k

—

k

—

—

k

k

Add literal and W

AND literal with W

Call subroutine

Clear Watchdog Timer

Go to address

Inclusive OR literal with W

Move literal to W

Return from interrupt

Return with literal in W

Return from Subroutine

Go into Standby mode

Subtract W from literal

Exclusive OR literal with W

1

1

2

1

2

1

1

2

2

2

1

1

1

11

11

10

00

10

11

11

00

11

00

00

11

11

111x

1001

0kkk

0000

1kkk

1000

00xx

0000

01xx

0000

0000

110x

1010

kkkk

kkkk

kkkk

0110

kkkk

kkkk

kkkk

0000

kkkk

0000

0110

kkkk

kkkk

kkkk

kkkk

kkkk

0100

kkkk

kkkk

kkkk

1001

kkkk

1000

0011

kkkk

kkkk

C,DC,Z

Z

TO,PD

Z

TO,PD

C,DC,Z

Z

Note

1:

When an I/O register is modified as a function of itself ( e.g.,

MOVF PORTB, 1

), the value used will be that value present on the

pins themselves. For example, if the data latch is ‘

1

’ for a pin configured as input and is driven low by an external device, the data

will be written back with a ‘

0

’.

2:

If this instruction is executed on the TMR0 register (and, where applicable, d =

1

), the prescaler will be cleared if assigned to the

Timer0 Module.

3:

If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed

as a

NOP

.

Summary of Contents for PIC16F716

Page 6: ...PIC16F716 DS41206A page 4 Preliminary 2003 Microchip Technology Inc NOTES...

Page 35: ......

Page 56: ......

Page 60: ......

Page 88: ......

Page 92: ...PIC16F716 DS41206A page 90 Preliminary 2003 Microchip Technology Inc NOTES...

Page 108: ...PIC16F716 DS41206A page 106 Preliminary 2003 Microchip Technology Inc NOTES...

Page 110: ...PIC16F716 DS41206A page 108 Preliminary 2003 Microchip Technology Inc NOTES...

Page 124: ...PIC16F716 DS41206A page 122 Preliminary 2003 Microchip Technology Inc NOTES...