2003 Microchip Technology Inc.

DS39582B-page 23

PIC16F87XA

2.2.2.2

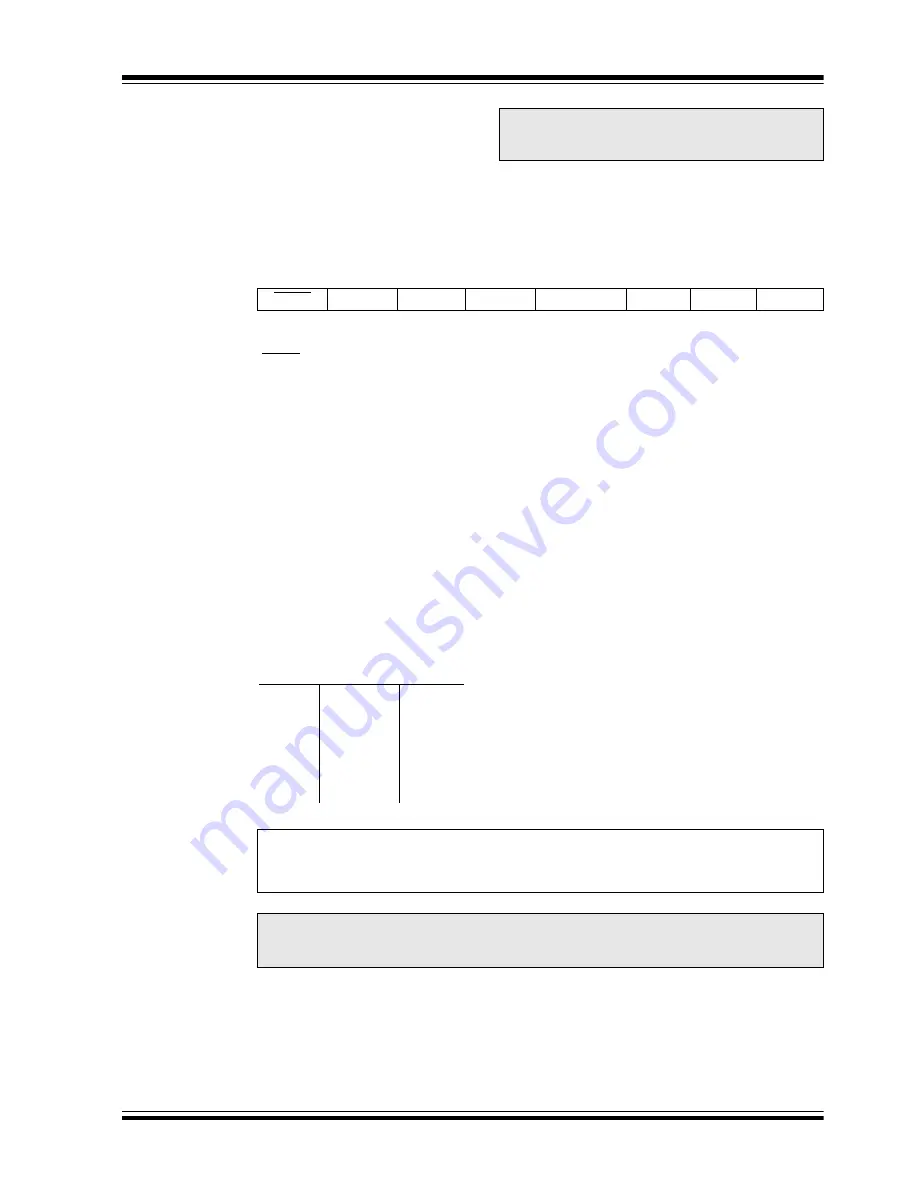

OPTION_REG Register

The OPTION_REG Register is a readable and writable

register, which contains various control bits to configure

the TMR0 prescaler/WDT postscaler (single assign-

able register known also as the prescaler), the external

INT interrupt, TMR0 and the weak pull-ups on PORTB.

REGISTER 2-2:

OPTION_REG REGISTER (ADDRESS 81h, 181h)

Note:

To achieve a 1:1 prescaler assignment for

the TMR0 register, assign the prescaler to

the Watchdog Timer.

R/W-1

R/W-1

R/W-1

R/W-1

R/W-1

R/W-1

R/W-1

R/W-1

RBPU

INTEDG

T0CS

T0SE

PSA

PS2

PS1

PS0

bit 7

bit 0

bit 7

RBPU: PORTB Pull-up Enable bit

1

= PORTB pull-ups are disabled

0

= PORTB pull-ups are enabled by individual port latch values

bit 6

INTEDG: Interrupt Edge Select bit

1

= Interrupt on rising edge of RB0/INT pin

0

= Interrupt on falling edge of RB0/INT pin

bit 5

T0CS: TMR0 Clock Source Select bit

1

= Transition on RA4/T0CKI pin

0

= Internal instruction cycle clock (CLKO)

bit 4

T0SE: TMR0 Source Edge Select bit

1

= Increment on high-to-low transition on RA4/T0CKI pin

0

= Increment on low-to-high transition on RA4/T0CKI pin

bit 3

PSA: Prescaler Assignment bit

1

= Prescaler is assigned to the WDT

0

= Prescaler is assigned to the Timer0 module

bit 2-0

PS2:PS0: Prescaler Rate Select bits

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

- n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

Note:

When using Low-Voltage ICSP Programming (LVP) and the pull-ups on PORTB are

enabled, bit 3 in the TRISB register must be cleared to disable the pull-up on RB3

and ensure the proper operation of the device

000

001

010

011

100

101

110

111

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

1 : 256

1 : 1

1 : 2

1 : 4

1 : 8

1 : 16

1 : 32

1 : 64

1 : 128

Bit Value

TMR0 Rate WDT Rate

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655