2003 Microchip Technology Inc.

DS39582B-page 27

PIC16F87XA

2.2.2.6

PIE2 Register

The PIE2 register contains the individual enable bits for

the CCP2 peripheral interrupt, the SSP bus collision

interrupt, EEPROM write operation interrupt and the

comparator interrupt.

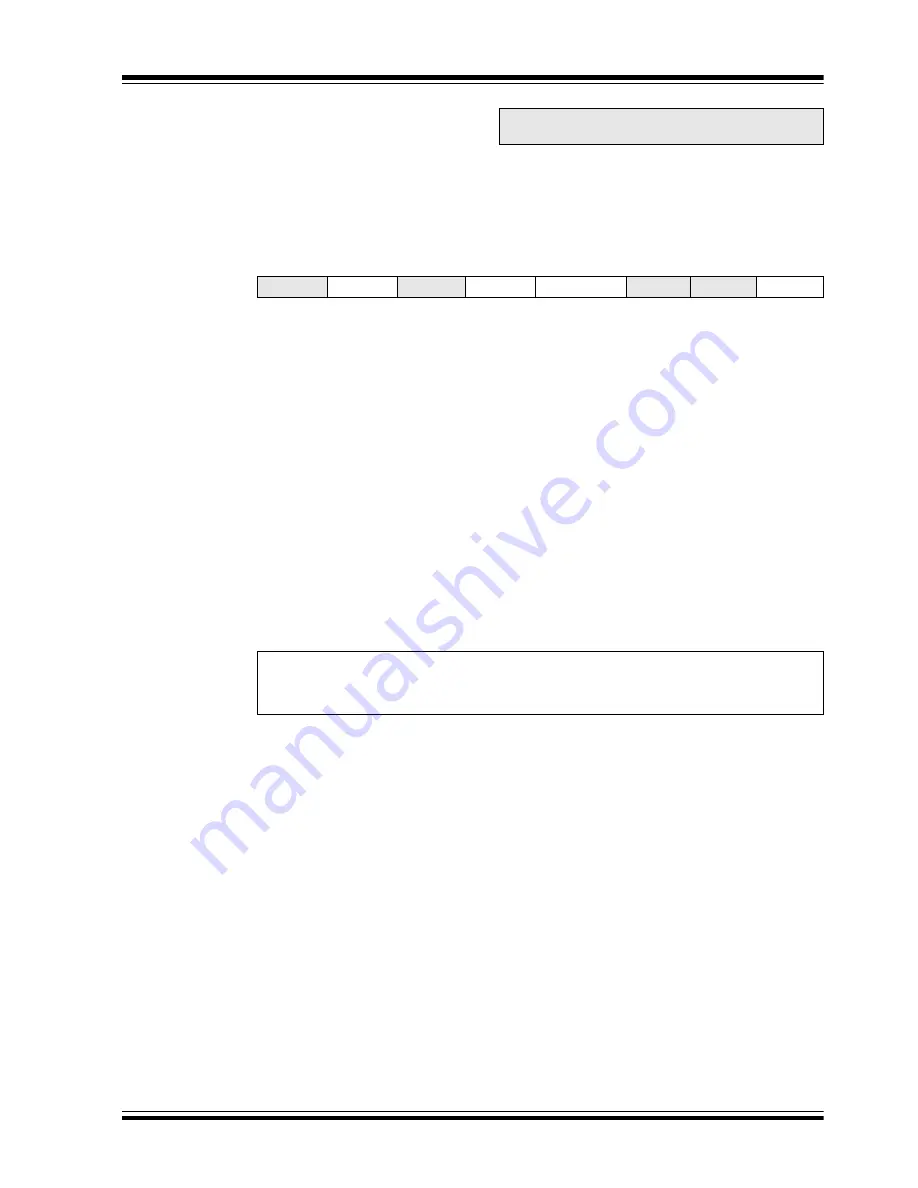

REGISTER 2-6:

PIE2 REGISTER (ADDRESS 8Dh)

Note:

Bit PEIE (INTCON<6>) must be set to

enable any peripheral interrupt.

U-0

R/W-0

U-0

R/W-0

R/W-0

U-0

U-0

R/W-0

—

CMIE

—

EEIE

BCLIE

—

—

CCP2IE

bit 7

bit 0

bit 7

Unimplemented: Read as ‘

0

’

bit 6

CMIE: Comparator Interrupt Enable bit

1

= Enables the comparator interrupt

0

= Disable the comparator interrupt

bit 5

Unimplemented: Read as ‘

0

’

bit 4

EEIE: EEPROM Write Operation Interrupt Enable bit

1

= Enable EEPROM write interrupt

0

= Disable EEPROM write interrupt

bit 3

BCLIE: Bus Collision Interrupt Enable bit

1

= Enable bus collision interrupt

0

= Disable bus collision interrupt

bit 2-1

Unimplemented: Read as ‘

0

’

bit 0

CCP2IE: CCP2 Interrupt Enable bit

1

= Enables the CCP2 interrupt

0

= Disables the CCP2 interrupt

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

- n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655