PIC16F87XA

DS39582B-page 44

2003 Microchip Technology Inc.

4.2

PORTB and the TRISB Register

PORTB is an 8-bit wide, bidirectional port. The corre-

sponding data direction register is TRISB. Setting a

TRISB bit (=

1

) will make the corresponding PORTB

pin an input (i.e., put the corresponding output driver in

a High-Impedance mode). Clearing a TRISB bit (=

0

)

will make the corresponding PORTB pin an output (i.e.,

put the contents of the output latch on the selected pin).

Three pins of PORTB are multiplexed with the In-Circuit

Debugger and Low-Voltage Programming function:

RB3/PGM, RB6/PGC and RB7/PGD. The alternate

functions of these pins are described in Section 14.0

“Special Features of the CPU”.

Each of the PORTB pins has a weak internal pull-up. A

single control bit can turn on all the pull-ups. This is per-

formed by clearing bit RBPU (OPTION_REG<7>). The

weak pull-up is automatically turned off when the port

pin is configured as an output. The pull-ups are

disabled on a Power-on Reset.

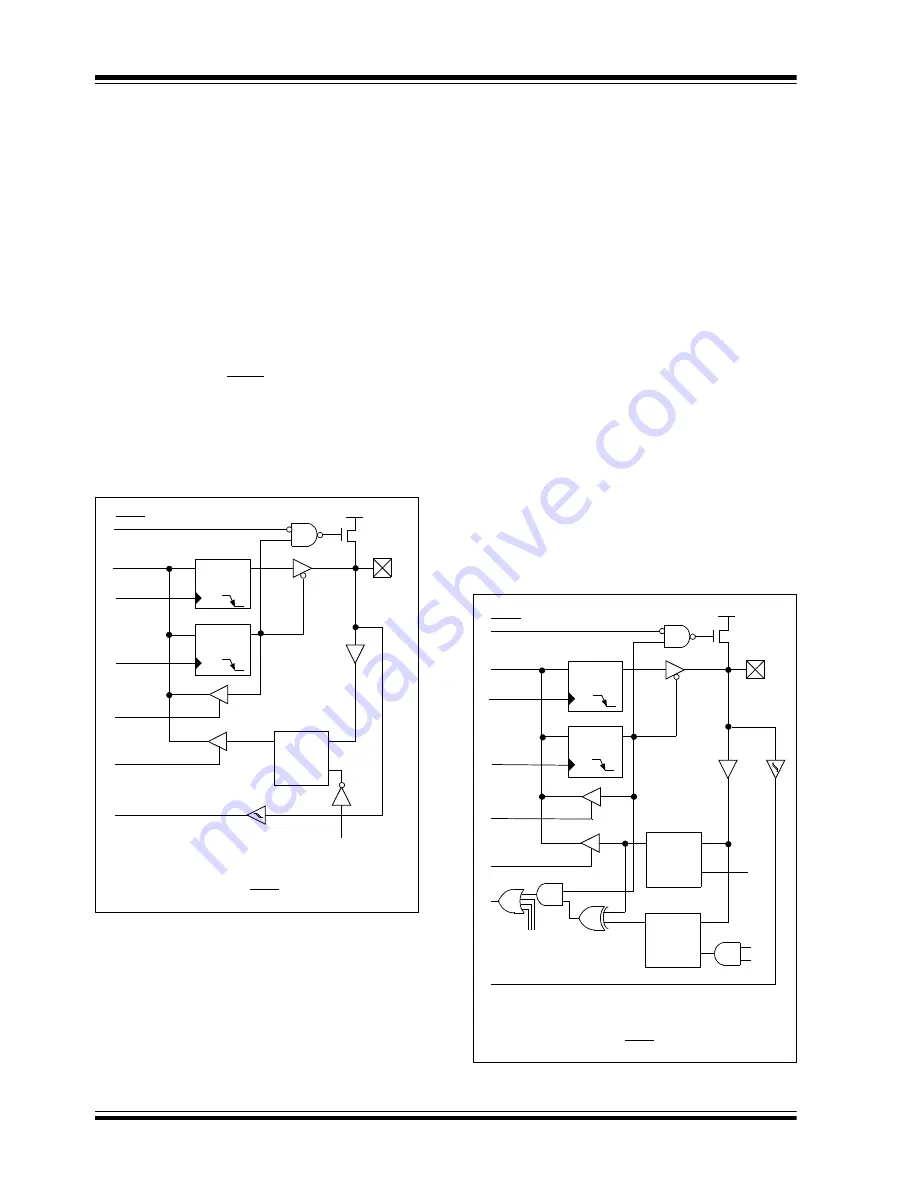

FIGURE 4-4:

BLOCK DIAGRAM OF

RB3:RB0 PINS

Four of the PORTB pins, RB7:RB4, have an interrupt-

on-change feature. Only pins configured as inputs can

cause this interrupt to occur (i.e., any RB7:RB4 pin

configured as an output is excluded from the interrupt-

on-change comparison). The input pins (of RB7:RB4)

are compared with the old value latched on the last

read of PORTB. The “mismatch” outputs of RB7:RB4

are OR’ed together to generate the RB port change

interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The

user, in the Interrupt Service Routine, can clear the

interrupt in the following manner:

a)

Any read or write of PORTB. This will end the

mismatch condition.

b)

Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF.

Reading PORTB will end the mismatch condition and

allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for

wake-up on key depression operation and operations

where PORTB is only used for the interrupt-on-change

feature. Polling of PORTB is not recommended while

using the interrupt-on-change feature.

This interrupt-on-mismatch feature, together with soft-

ware configurable pull-ups on these four pins, allow

easy interface to a keypad and make it possible for

wake-up on key depression. Refer to the application

note, AN552, “Implementing Wake-up on Key Stroke”

(DS00552).

RB0/INT is an external interrupt input pin and is

configured using the INTEDG bit (OPTION_REG<6>).

RB0/INT is discussed in detail in Section 14.11.1 “INT

Interrupt”.

FIGURE 4-5:

BLOCK DIAGRAM OF

RB7:RB4 PINS

Data Latch

RBPU

(2)

P

V

DD

Q

D

CK

Q

D

CK

Q

D

EN

Data Bus

WR Port

WR TRIS

RD TRIS

RD Port

Weak

Pull-up

RD Port

RB0/INT

I/O pin

(1)

TTL

Input

Buffer

Schmitt Trigger

Buffer

TRIS Latch

Note 1: I/O pins have diode protection to V

DD

and V

SS

.

2: To enable weak pull-ups, set the appropriate TRIS

bit(s) and clear the RBPU bit (OPTION_REG<7>).

RB3/PGM

Data Latch

From other

RBPU

(2)

P

V

DD

I/O pin

(1)

Q

D

CK

Q

D

CK

Q

D

EN

Q

D

EN

Data Bus

WR Port

WR TRIS

Set RBIF

TRIS Latch

RD TRIS

RD Port

RB7:RB4 pins

Weak

Pull-up

RD Port

Latch

TTL

Input

Buffer

ST

Buffer

RB7:RB6

Q3

Q1

Note 1: I/O pins have diode protection to V

DD

and V

SS

.

2: To enable weak pull-ups, set the appropriate TRIS

bit(s) and clear the RBPU bit (OPTION_REG<7>).

In Serial Programming Mode

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655