2003 Microchip Technology Inc.

DS39582B-page 53

PIC16F87XA

5.0

TIMER0 MODULE

The Timer0 module timer/counter has the following

features:

• 8-bit timer/counter

• Readable and writable

• 8-bit software programmable prescaler

• Internal or external clock select

• Interrupt on overflow from FFh to 00h

• Edge select for external clock

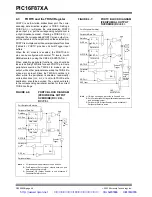

Figure 5-1 is a block diagram of the Timer0 module and

the prescaler shared with the WDT.

Additional information on the Timer0 module is

available in the PICmicro

®

Mid-Range MCU Family

Reference Manual (DS33023).

Timer mode is selected by clearing bit T0CS

(OPTION_REG<5>). In Timer mode, the Timer0

module will increment every instruction cycle (without

prescaler). If the TMR0 register is written, the incre-

ment is inhibited for the following two instruction cycles.

The user can work around this by writing an adjusted

value to the TMR0 register.

Counter mode is selected by setting bit T0CS

(OPTION_REG<5>). In Counter mode, Timer0 will

increment either on every rising or falling edge of pin

RA4/T0CKI. The incrementing edge is determined by

the Timer0 Source Edge Select bit, T0SE

(OPTION_REG<4>). Clearing bit T0SE selects the ris-

ing edge. Restrictions on the external clock input are

discussed in detail in Section 5.2 “Using Timer0 with

an External Clock”.

The prescaler is mutually exclusively shared between

the Timer0 module and the Watchdog Timer. The

prescaler is not readable or writable. Section 5.3

“Prescaler” details the operation of the prescaler.

5.1

Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0

register overflows from FFh to 00h. This overflow sets

bit TMR0IF (INTCON<2>). The interrupt can be

masked by clearing bit TMR0IE (INTCON<5>). Bit

TMR0IF must be cleared in software by the Timer0

module Interrupt Service Routine before re-enabling

this interrupt. The TMR0 interrupt cannot awaken the

processor from Sleep since the timer is shut-off during

Sleep.

FIGURE 5-1:

BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

RA4/T0CKI

T0SE

pin

M

U

X

CLKO (= F

OSC

/4)

Sync

2

Cycles

TMR0 Reg

8-bit Prescaler

8-to-1 MUX

M

U

X

MUX

Watchdog

Timer

PSA

0

1

0

1

WDT

Time-out

PS2:PS0

8

Note: T0CS, T0SE, PSA, PS2:PS0 are (OPTION_REG<5:0>).

PSA

WDT Enable bit

M

U

X

0

1

0

1

Data Bus

Set Flag bit TMR0IF

on Overflow

8

PSA

T0CS

PRESCALER

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655