2003 Microchip Technology Inc.

DS39582B-page 59

PIC16F87XA

6.4

Timer1 Operation in

Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external

clock input is not synchronized. The timer continues to

increment asynchronous to the internal phase clocks.

The timer will continue to run during Sleep and can

generate an interrupt-on-overflow which will wake-up

the processor. However, special precautions in

software are needed to read/write the timer.

In Asynchronous Counter mode, Timer1 cannot be

used as a time base for capture or compare operations.

6.4.1

READING AND WRITING TIMER1 IN

ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running

from an external asynchronous clock will ensure a valid

read (taken care of in hardware). However, the user

should keep in mind that reading the 16-bit timer in two

8-bit values itself, poses certain problems, since the

timer may overflow between the reads.

For writes, it is recommended that the user simply stop

the timer and write the desired values. A write conten-

tion may occur by writing to the timer registers while the

register is incrementing. This may produce an

unpredictable value in the timer register.

Reading the 16-bit value requires some care.

Examples 12-2 and 12-3 in the PICmicro

®

Mid-Range

MCU Family Reference Manual (DS33023) show how

to read and write Timer1 when it is running in

Asynchronous mode.

6.5

Timer1 Oscillator

A crystal oscillator circuit is built-in between pins T1OSI

(input) and T1OSO (amplifier output). It is enabled by

setting control bit, T1OSCEN (T1CON<3>). The oscil-

lator is a low-power oscillator, rated up to 200 kHz. It

will continue to run during Sleep. It is primarily intended

for use with a 32 kHz crystal. Table 6-1 shows the

capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is identical to the LP oscillator.

The user must provide a software time delay to ensure

proper oscillator start-up.

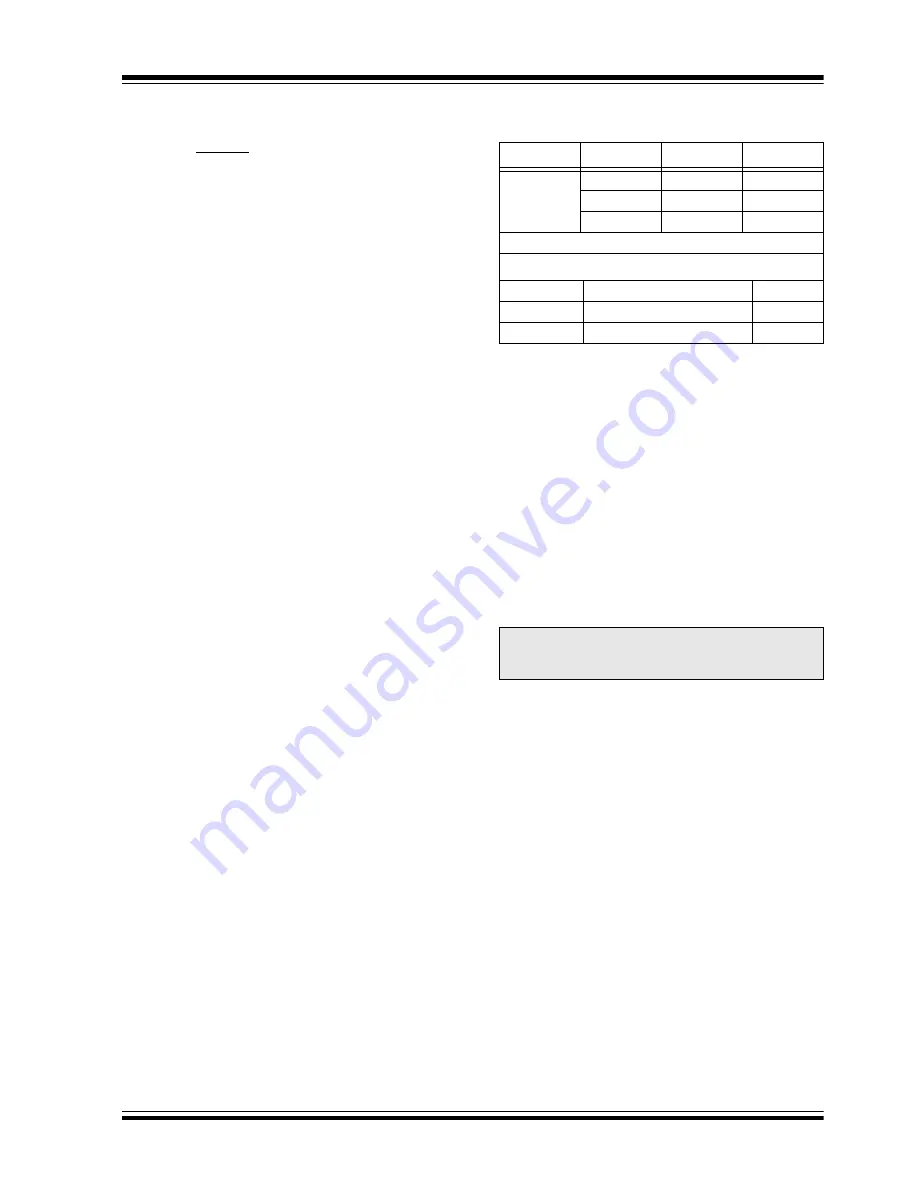

TABLE 6-1:

CAPACITOR SELECTION FOR

THE TIMER1 OSCILLATOR

6.6

Resetting Timer1 Using a CCP

Trigger Output

If the CCP1 or CCP2 module is configured in Compare

mode to generate a “special event trigger”

(CCP1M3:CCP1M0 =

1011

), this signal will reset

Timer1.

Timer1 must be configured for either Timer or Synchro-

nized Counter mode to take advantage of this feature.

If Timer1 is running in Asynchronous Counter mode,

this Reset operation may not work.

In the event that a write to Timer1 coincides with a

special event trigger from CCP1 or CCP2, the write will

take precedence.

In this mode of operation, the CCPRxH:CCPRxL regis-

ter pair effectively becomes the period register for

Timer1.

Osc Type

Freq.

C1

C2

LP

32 kHz

33 pF

33 pF

100 kHz

15 pF

15 pF

200 kHz

15 pF

15 pF

These values are for design guidance only.

Crystals Tested:

32.768 kHz

Epson C-001R32.768K-A

± 20 PPM

100 kHz

Epson C-2 100.00 KC-P

± 20 PPM

200 kHz

STD XTL 200.000 kHz

± 20 PPM

Note 1:

Higher capacitance increases the stability

of oscillator but also increases the start-up

time.

2:

Since each resonator/crystal has its own

characteristics, the user should consult

the resonator/crystal manufacturer for

appropriate values of external

components.

Note:

The special event triggers from the CCP1

and CCP2 modules will not set interrupt

flag bit, TMR1IF (PIR1<0>).

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655