PIC16F87XA

DS39582B-page 62

2003 Microchip Technology Inc.

7.1

Timer2 Prescaler and Postscaler

The prescaler and postscaler counters are cleared

when any of the following occurs:

• a write to the TMR2 register

• a write to the T2CON register

• any device Reset (POR, MCLR Reset, WDT

Reset or BOR)

TMR2 is not cleared when T2CON is written.

7.2

Output of TMR2

The output of TMR2 (before the postscaler) is fed to the

SSP module, which optionally uses it to generate the

shift clock.

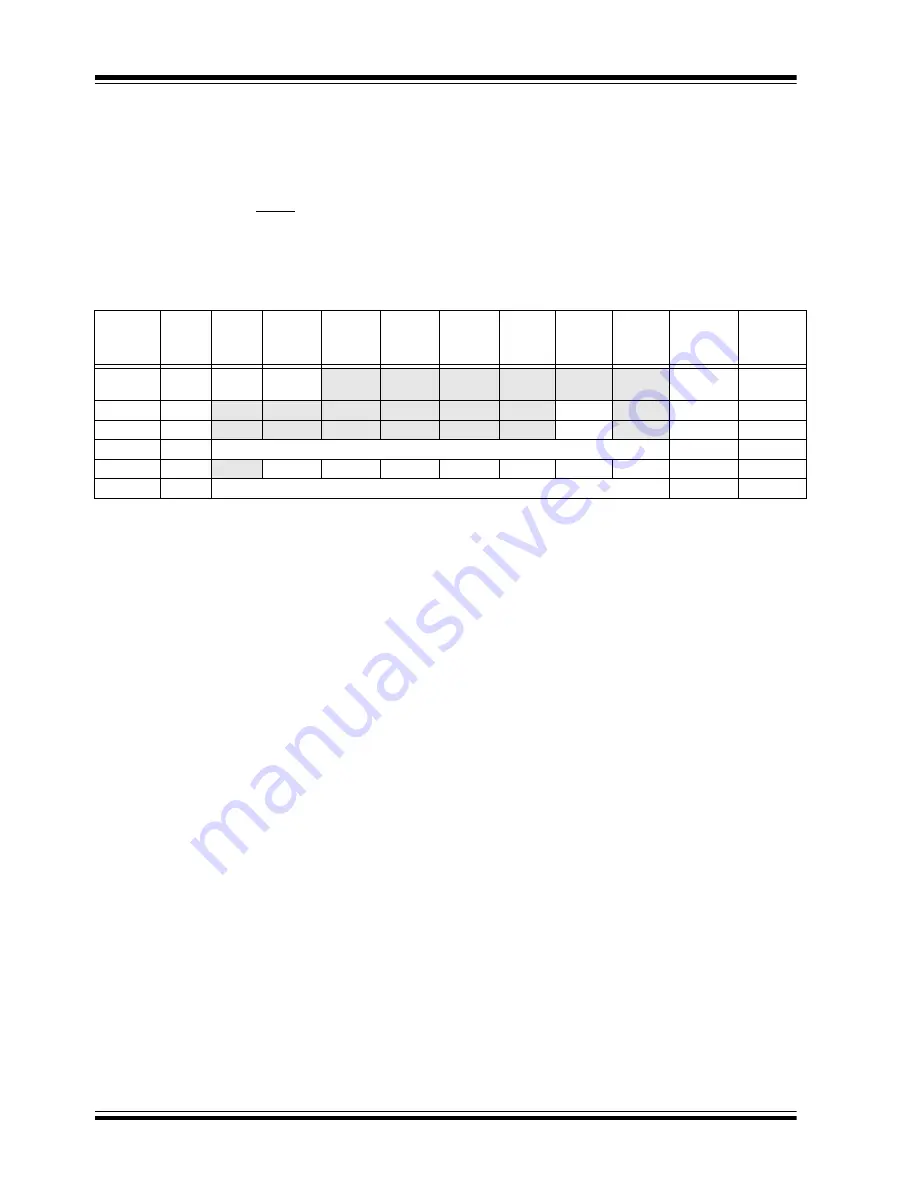

TABLE 7-1:

REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on:

POR, BOR

Value on

all other

Resets

0Bh, 8Bh,

10Bh, 18Bh

INTCON

GIE

PEIE

TMR0IE

INTE

RBIE

TMR0IF

INTF

RBIF

0000 000x 0000 000u

0Ch

PIR1

PSPIF

(1)

ADIF

RCIF

TXIF

SSPIF

CCP1IF

TMR2IF

TMR1IF

0000 0000 0000 0000

8Ch

PIE1

PSPIE

(1)

ADIE

RCIE

TXIE

SSPIE

CCP1IE

TMR2IE

TMR1IE

0000 0000 0000 0000

11h

TMR2

Timer2 Module’s Register

0000 0000 0000 0000

12h

T2CON

—

TOUTPS3 TOUTPS2 TOUTPS1 TOUTPS0 TMR2ON T2CKPS1 T2CKPS0

-000 0000 -000 0000

92h

PR2

Timer2 Period Register

1111 1111 1111 1111

Legend:

x

= unknown,

u

= unchanged,

-

= unimplemented, read as ‘

0

’. Shaded cells are not used by the Timer2 module.

Note

1:

Bits PSPIE and PSPIF are reserved on 28-pin devices; always maintain these bits clear.

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655