2003 Microchip Technology Inc.

DS39582B-page 93

PIC16F87XA

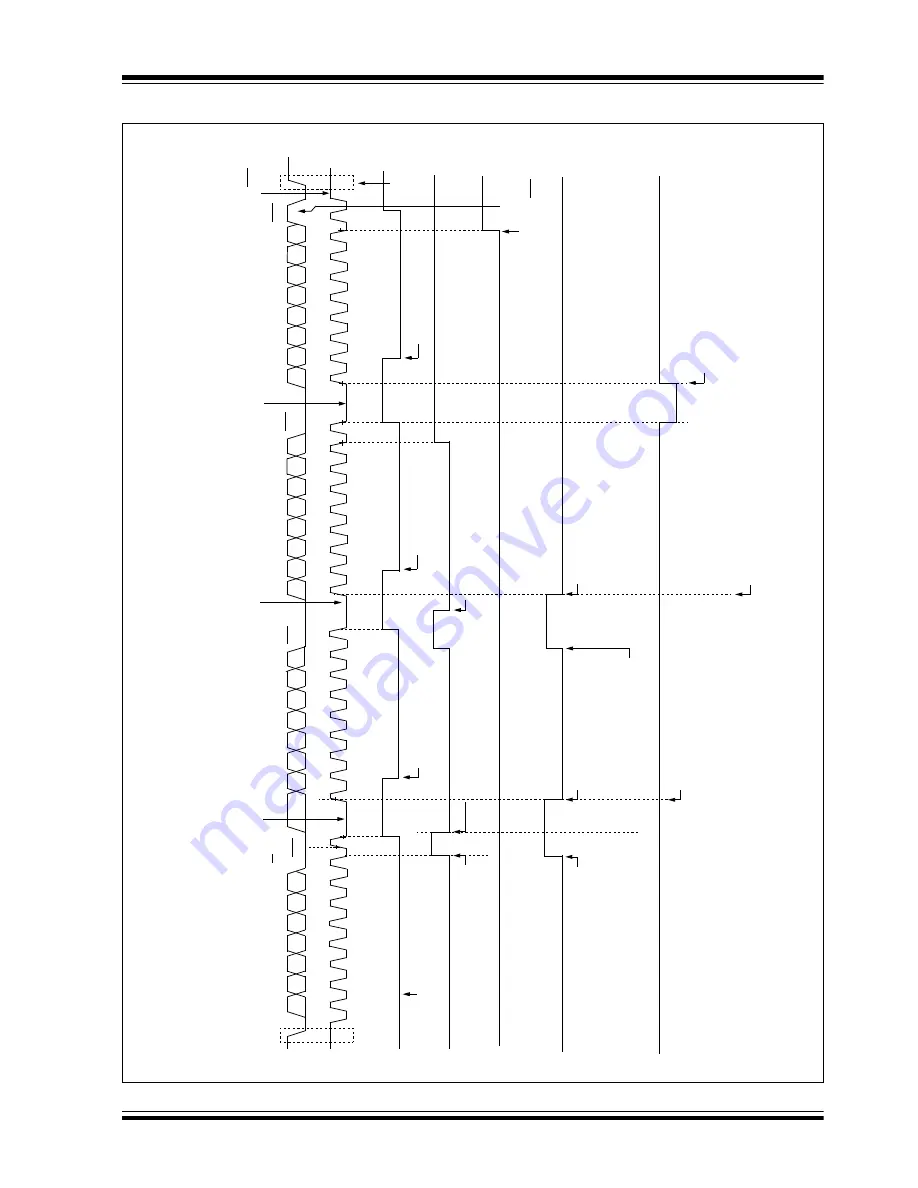

FIGURE 9-14:

I

2

C SLAVE MODE TIMING SEN =

1

(RECEPTION, 10-BIT ADDRESS)

SD

A

SC

L

S

SPI

F

B

F

(

SSP

ST

A

T

<0

>)

S

1

2

3

4

5

6

7

8

9

1

23

4

5

6

7

89

1

2

3

4

5

7

8

9

P

1

1

1

1

0

A

9A

8

A

7

A

6

A

5

A

4

A

3

A

2A

1

A

0

D

7D

6D

5

D

4

D

3

D

1

D

0

Re

ce

ive

Da

ta

Byte

ACK

R/W

=

0

ACK

R

ecei

v

e

Fi

rst

B

y

te

of A

ddr

ess

Cle

a

re

d

in

so

ft

wa

re

D2

6

(P

IR

1<

3>

)

Cle

a

re

d

in

so

ft

wa

re

R

e

cei

v

e

S

e

cond B

y

te o

f A

ddre

s

s

C

leare

d by ha

rdw

ar

e w

hen

S

S

P

A

D

D

i

s

upd

ated

w

ith

l

o

w

byte o

f addr

ess aft

e

r fa

lli

n

g

edge

U

A

(

S

SP

S

T

A

T

<1

>)

Clo

ck is h

e

ld

lo

w u

n

til

u

pdate

of S

S

P

A

D

D

h

a

s

ta

ke

n pl

ace

UA

is se

t indicating

that

S

S

P

A

D

D

nee

ds to b

e

updat

ed

UA

is set indica

ting tha

t

S

S

P

A

D

D

n

eeds to

be

upd

ated

C

lea

red b

y

har

dw

are

w

h

en

S

S

P

A

D

D

i

s

updat

ed w

it

h h

ig

h

by

te of a

ddre

ss after

fal

ling e

dge

S

SPB

UF

is wr

itte

n

with

conten

ts

of S

S

P

S

R

Du

m

m

y

r

e

a

d

o

f SSP

BUF

to clea

r B

F

fla

g

ACK

CK

P

12

3

4

5

7

8

9

D7

D6

D5

D4

D3

D1

D0

Re

ce

ive

Da

ta

B

yt

e

B

u

s m

a

ste

r

ter

m

inate

s

tra

n

sfer

D2

6

ACK

C

lea

re

d i

n

s

o

ft

w

ar

e

Cle

a

re

d

in

so

ft

w

a

re

SSP

O

V

(

SSP

CO

N

<

6

>

)

CK

P

writte

n to ‘

1

’

No

te

:

A

n updat

e

of the

S

S

P

A

D

D

reg

ist

er

b

e

for

e

t

he fal

ling edge

o

f

th

e ni

nth cl

ock

will h

a

ve

n

o

e

ffe

ct o

n

UA, a

n

d

UA will

re

ma

in

set.

No

te

:

A

n

upda

te of

the S

S

P

A

D

D

regi

ste

r

befo

re the fal

ling edg

e

o

f

th

e

n

inth cl

ock

wil

l have

no

e

ffect on UA

and UA

will

rem

a

in set.

in softwar

e

Clo

ck is h

e

ld

lo

w u

n

ti

l

upd

ate of

S

S

P

A

D

D

has

ta

ken pl

ace

of

ni

nth cl

o

c

k

of ni

nt

h cl

ock

SSP

O

V

is

s

e

t

b

e

cause S

S

P

B

U

F

i

s

still fu

ll.

A

C

K

i

s

not

sent.

Du

m

m

y

r

e

a

d

o

f SSP

BUF

to clea

r B

F

flag

Clo

ck is h

e

ld

lo

w u

n

til

CK

P

is set to

‘

1

’

C

lo

ck i

s

not

hel

d l

o

w

becau

se A

C

K

=

1

http://www.xinpian.net

提供单片机解密、IC解密、芯片解密业务

010-62245566 13810019655