2013 Microchip Technology Inc.

Advance Information

DS33030A-page 165

PIC24FV16KM204 FAMILY

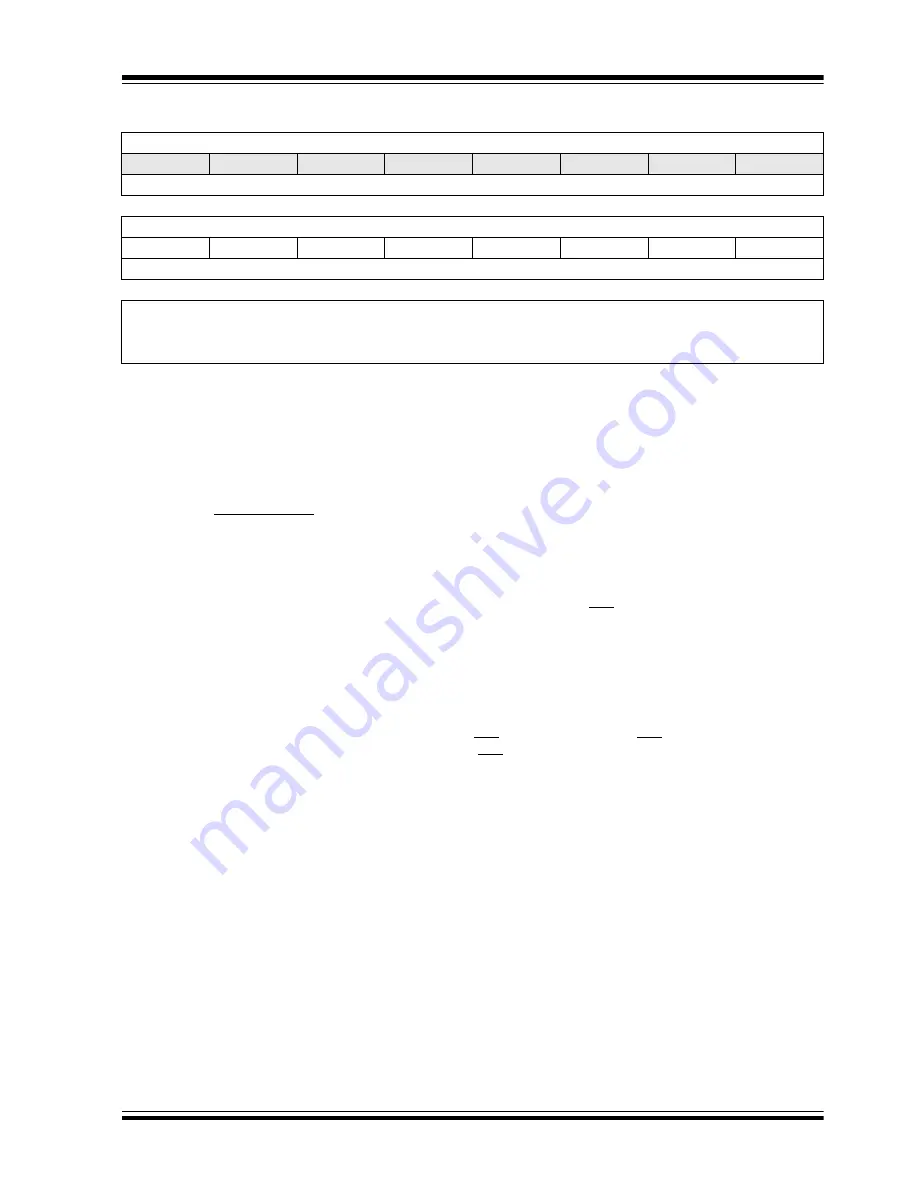

REGISTER 14-3:

SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

U-0

U-0

U-0

U-0

U-0

U-0

U-0

U-0

—

—

—

—

—

—

—

—

bit 15

bit 8

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

WCOL

SSPOV

)

SSPEN

(

CKP

SSPM3

)

SSPM2

SSPM1

(

SSPM0

(

bit 7

bit 0

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 15-8

Unimplemented:

Read as ‘

0

’

bit 7

WCOL:

Write Collision Detect bit

1

= The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in

software)

0

= No collision

bit 6

SSPOV:

Master Synchronous Serial Port Receive Overflow Indicator bit

)

SPI Slave mode:

1

= A new byte is received while the SSPxBUF register is still holding the previous data. In case of over-

flow, the data in SSPxSR is lost. Overflow can only occur in Slave mode. The user must read the

SSPxBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).

0

= No overflow

bit 5

SSPEN:

Master Synchronous Serial Port Enable bit

)

1

= Enables serial port and configures SCKx, SDOx, SDIx and SSx as serial port pins

0

= Disables serial port and configures these pins as I/O port pins

bit 4

CKP:

Clock Polarity Select bit

1

= Idle state for clock is a high level

0

= Idle state for clock is a low level

bit 3-0

SSPM<3:0>:

Master Synchronous Serial Port Mode Select bits

(

1010

= SPI Master mode, Clock =

F

OSC

/(2 * ([SSPxADD] + 1))

0101

= SPI Slave mode, Clock = SCKx pin; SSx pin control is disabled, SSx can be used as an I/O pin

0100

= SPI Slave mode, Clock = SCKx pin; SSx pin control is enabled

0011

= SPI Master mode, Clock = TMR2 output/2

0010

= SPI Master mode, Clock = F

OSC

/32

0001

= SPI Master mode, Clock = F

OSC

/8

0000

= SPI Master mode, Clock = F

OSC

/2

Note 1:

In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by

writing to the SSPxBUF register.

2:

When enabled, these pins must be properly configured as inputs or outputs.

3:

Bit combinations not specifically listed here are either reserved or implemented in I

2

C™ mode only.

Summary of Contents for PIC24FV16KM204 FAMILY

Page 312: ...PIC24FV16KM204 FAMILY DS33030A page 312 Advance Information 2013 Microchip Technology Inc ...

Page 313: ... 2013 Microchip Technology Inc Advance Information DS33030A page 313 PIC24FV16KM204 FAMILY ...

Page 315: ... 2013 Microchip Technology Inc Advance Information DS33030A page 315 PIC24FV16KM204 FAMILY ...

Page 316: ...PIC24FV16KM204 FAMILY DS33030A page 316 Advance Information 2013 Microchip Technology Inc ...

Page 317: ... 2013 Microchip Technology Inc Advance Information DS33030A page 317 PIC24FV16KM204 FAMILY ...

Page 322: ...PIC24FV16KM204 FAMILY DS33030A page 322 Advance Information 2013 Microchip Technology Inc ...