2013 Microchip Technology Inc.

Advance Information

DS33030A-page 151

PIC24FV16KM204 FAMILY

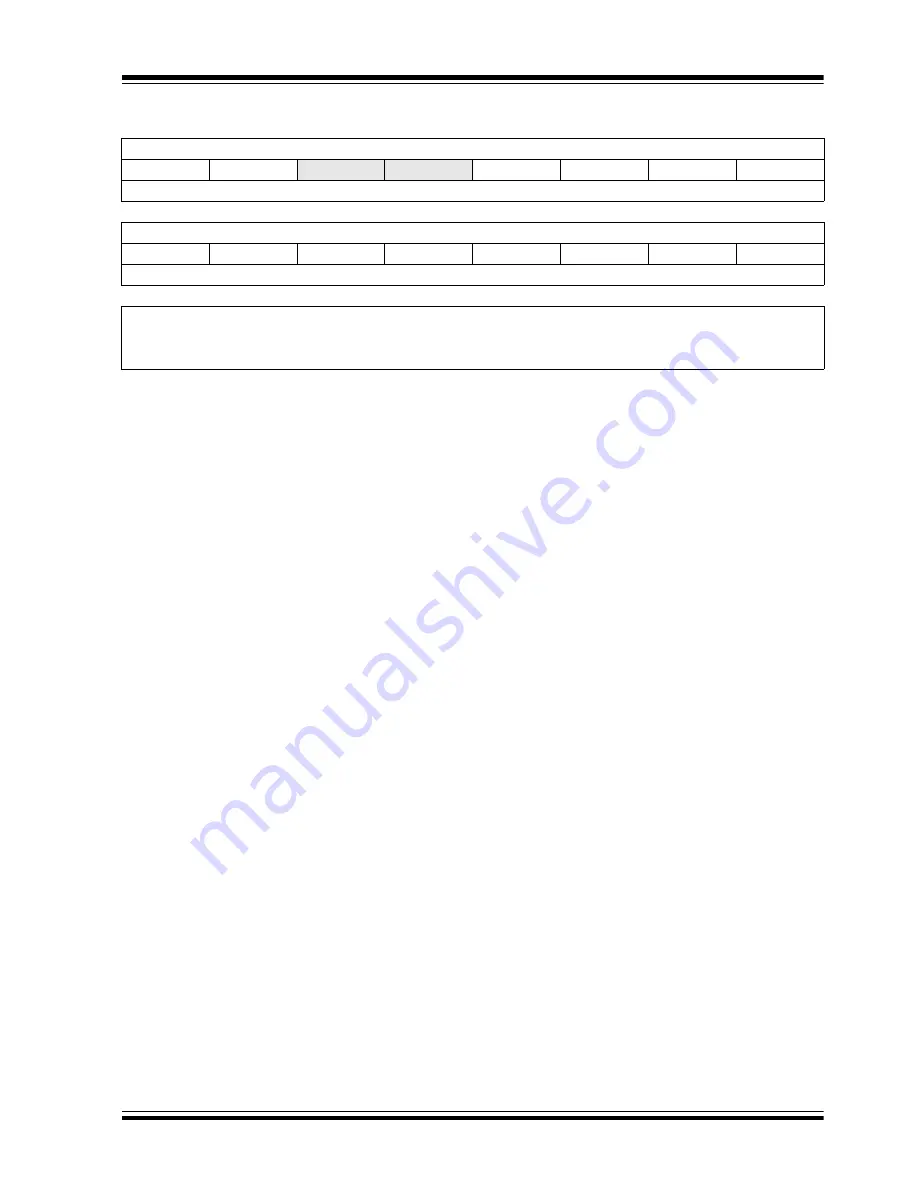

REGISTER 13-2:

CCPxCON1H: CCPx CONTROL 1 HIGH REGISTERS

R/W-0

R/W-0

U-0

U-0

R/W-0

R/W-0

R/W-0

R/W-0

OPSSRC

(

RTRGEN

—

—

OPS3

OPS2

OPS1

OPS0

bit 15

bit 8

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

TRIGEN

ONESHOT

ALTSYNC

(

SYNC4

SYNC3

SYNC2

SYNC1

SYNC0

bit 7

bit 0

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 15

OPSSRC:

Output Postscaler Source Select bit

)

1

= Output postscaler scales module Trigger output events

0

= Output postscaler scales time base interrupt events

bit 14

RTRGEN:

Retrigger Enable bit

(

1

= Time base can be retriggered when TRIG bit =

1

0

= Time base may not be retriggered when TRIG bit =

1

bit 13-12

Unimplemented:

Read as ‘

0

’

bit 11-8

OPS3<3:0>:

CCPx Interrupt Output Postscale Select bits

(3)

1111

= Interrupt every 16th time base period match

1110

= Interrupt every 15th time base period match

. . .

0100

= Interrupt every 5th time base period match

0011

= Interrupt every 4th time base period match or 4th input capture event

0010

= Interrupt every 3rd time base period match or 3rd input capture event

0001

= Interrupt every 2nd time base period match or 2nd input capture event

0000

= Interrupt after each time base period match or input capture event

bit 7

TRIGEN:

CCPx Trigger Enable bit

1

= Trigger operation of time base is enabled

0

= Trigger operation of time base is disabled

bit 6

ONESHOT:

One-Shot Mode Enable bit

1

= One-Shot Trigger mode is enabled; Trigger duration is set by OSCNT<2:0>

0

= One-Shot Trigger mode disabled

bit 5

ALTSYNC:

Capture/Compare/PWMx Clock Select bits

(

1

= An alternate signal is used as the module synchronization output signal

0

= The module synchronization output signal is the Time Base Reset/rollover event

bit 4-0

SYNC<4:0>:

CCPx Synchronization Source Select bits

See

for the definition of inputs.

Note 1:

This control bit has no function in Input Capture modes.

2:

This control bit has no function when TRIGEN =

0

.

3:

Output postscale settings from 1:5 to 1:16 (

0100

-

1111

) will result in a FIFO buffer overflow for Input Capture

modes.

Summary of Contents for PIC24FV16KM204 FAMILY

Page 312: ...PIC24FV16KM204 FAMILY DS33030A page 312 Advance Information 2013 Microchip Technology Inc ...

Page 313: ... 2013 Microchip Technology Inc Advance Information DS33030A page 313 PIC24FV16KM204 FAMILY ...

Page 315: ... 2013 Microchip Technology Inc Advance Information DS33030A page 315 PIC24FV16KM204 FAMILY ...

Page 316: ...PIC24FV16KM204 FAMILY DS33030A page 316 Advance Information 2013 Microchip Technology Inc ...

Page 317: ... 2013 Microchip Technology Inc Advance Information DS33030A page 317 PIC24FV16KM204 FAMILY ...

Page 322: ...PIC24FV16KM204 FAMILY DS33030A page 322 Advance Information 2013 Microchip Technology Inc ...