PIC24FV16KM204 FAMILY

DS33030A-page 198

Advance Information

2013 Microchip Technology Inc.

17.1

Control Registers

The CLCx module is controlled by the following registers:

• CLCxCONL

• CLCxCONH

• CLCxSEL

• CLCxGLSL

• CLCxGLSH

The CLCx Control registers (CLCxCONL and

CLCxCONH) are used to enable the module and inter-

rupts, control the output enable bit, select output polarity

and select the logic function. The CLCx Control registers

also allow the user to control the logic polarity of not only

the cell output, but also some intermediate variables.

The CLCx Source Select register (CLCxSEL) allows

the user to select up to 4 data input sources using the

4 data input selection multiplexers. Each multiplexer

has a list of 8 data sources available.

The CLCx Gate Logic Select registers (CLCxGLSL and

CLCxGLSH) allow the user to select which outputs

from each of the selection MUXes are used as inputs to

the input gates of the logic cell. Each data source MUX

outputs both a true and a negated version of its output.

All of these 8 signals are enabled, ORed together by

the logic cell input gates.

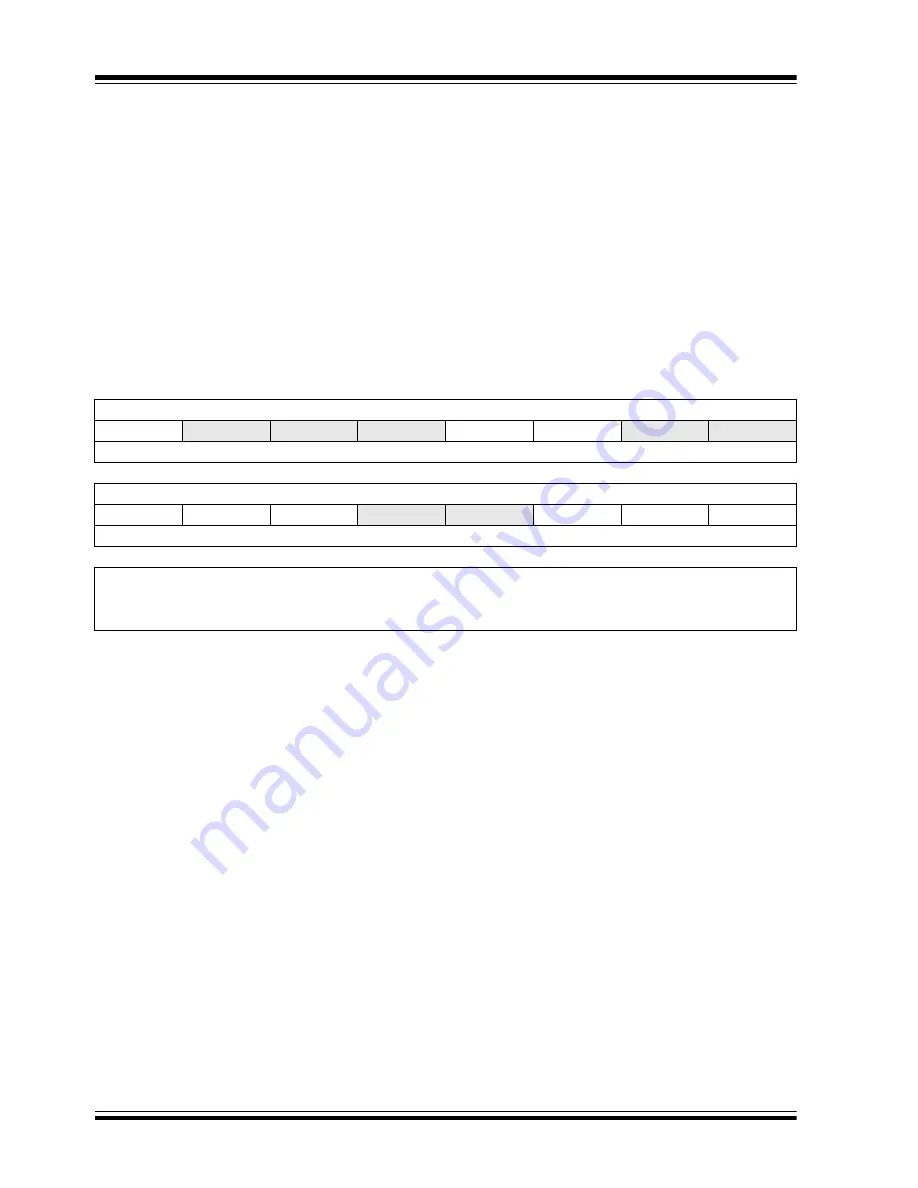

REGISTER 17-1:

CLCxCONL: CLCx CONTROL REGISTER (LOW)

R/W-0

U-0

U-0

U-0

R/W-0

R/W-0

U-0

U-0

LCEN

—

—

—

INTP

INTN

—

—

bit 15

bit 8

R-0

R-0

R/W-0

U-0

U-0

R/W-0

R/W-0

R/W-0

LCOE

LCOUT

LCPOL

—

—

MODE2

MODE1

MODE0

bit 7

bit 0

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as ‘0’

-n = Value at POR

‘1’ = Bit is set

‘0’ = Bit is cleared

x = Bit is unknown

bit 15

LCEN:

CLCx Enable bit

1

= CLCx is enabled and mixing input signals

0

= CLCx is disabled and has logic zero outputs

bit 14-12

Unimplemented:

Read as ‘

0

’

bit 11

INTP:

CLCx Positive Edge Interrupt Enable bit

1

= Interrupt will be generated when a rising edge occurs on LCOUT

0

= Interrupt will not be generated

bit 10

INTN:

CLCx Negative Edge Interrupt Enable bit

1

= Interrupt will be generated when a falling edge occurs on LCOUT

0

= Interrupt will not be generated

bit 9-8

Unimplemented:

Read as ‘

0

’

bit 7

LCOE:

CLCx Port Enable bit

1

= CLCx port pin output is enabled

0

= CLCx port pin output is disabled

bit 6

LCOUT:

CLCx Data Output Status bit

1

= CLCx output high

0

= CLCx output low

bit 5

LCPOL:

CLCx Output Polarity Control bit

1

= The output of the module is inverted

0

= The output of the module is not inverted

bit 4-3

Unimplemented:

Read as ‘

0

’

Summary of Contents for PIC24FV16KM204 FAMILY

Page 312: ...PIC24FV16KM204 FAMILY DS33030A page 312 Advance Information 2013 Microchip Technology Inc ...

Page 313: ... 2013 Microchip Technology Inc Advance Information DS33030A page 313 PIC24FV16KM204 FAMILY ...

Page 315: ... 2013 Microchip Technology Inc Advance Information DS33030A page 315 PIC24FV16KM204 FAMILY ...

Page 316: ...PIC24FV16KM204 FAMILY DS33030A page 316 Advance Information 2013 Microchip Technology Inc ...

Page 317: ... 2013 Microchip Technology Inc Advance Information DS33030A page 317 PIC24FV16KM204 FAMILY ...

Page 322: ...PIC24FV16KM204 FAMILY DS33030A page 322 Advance Information 2013 Microchip Technology Inc ...