USB5744

DS00001855E-page 36

2015-2017 Microchip Technology Inc.

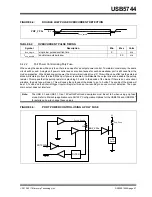

9.6.7

SPI TIMING

This section specifies the SPI timing requirements for the device.

FIGURE 9-5:

SPI TIMING

TABLE 9-8:

SPI TIMING (30 MHZ OPERATION)

Symbol

Description

Min

Typ

Max

Units

t

fc

Clock frequency

30

MHz

t

ceh

Chip enable (

SPI_CE_EN

) high time

100

ns

t

clq

Clock to input data

13

ns

t

dh

Input data hold time

0

ns

t

os

Output setup time

5

ns

t

oh

Output hold time

5

ns

t

ov

Clock to output valid

4

ns

t

cel

Chip enable (

SPI_CE_EN

) low to first clock

12

ns

t

ceh

Last clock to chip enable (

SPI_CE_EN

) high

12

ns

TABLE 9-9:

SPI TIMING (60 MHZ OPERATION)

Symbol

Description

Min

Typ

Max

Units

t

fc

Clock frequency

60

MHz

t

ceh

Chip enable (

SPI_CE_EN

) high time

50

ns

t

clq

Clock to input data

9

ns

t

dh

Input data hold time

0

ns

t

os

Output setup time

5

ns

t

oh

Output hold time

5

ns

t

ov

Clock to output valid

4

ns

t

cel

Chip enable (

SPI_CE_EN

) low to first clock

12

ns

t

ceh

Last clock to chip enable (

SPI_CE_EN

) high

12

ns

SPI_CLK

SPI_DI

SPI_DO

SPI_CE_N

t

cel

t

fc

t

clq

t

ceh

t

dh

t

oh

t

os

t

ov

t

oh