System Core, Boot Configuration and On-Board Memory 5

miriac SBC-LS1046A-TSN_User Manual

V 2.0

28/68

© MicroSys Electronics GmbH 20178

5.6

NAND Flash

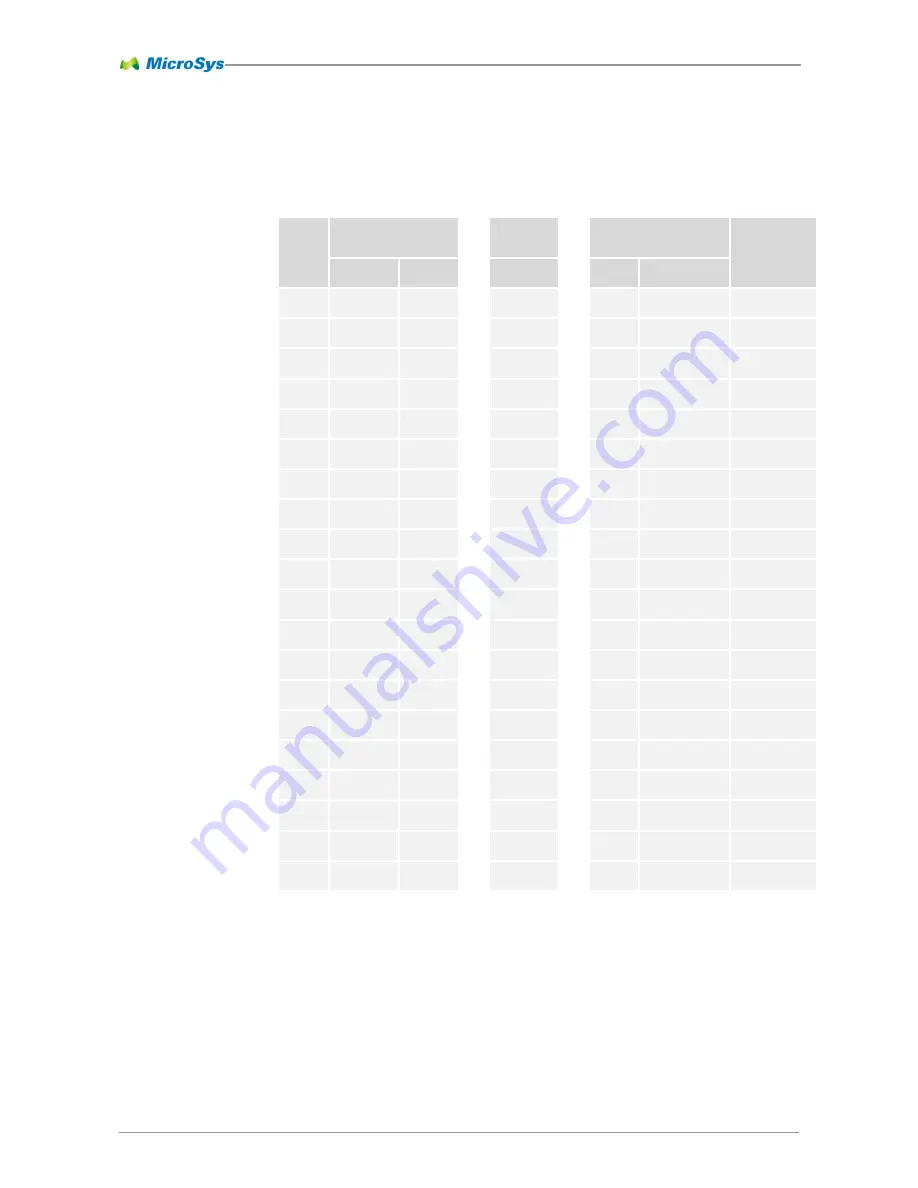

The SBC-LS1046A-TSN system is equipped with 2GB of NAND Flash by default.

Different sizes may be available on request/order. The following table shows the

connections and signal levels for the NAND Flash.

I/O

Range

NAND Flash

SBC-

LS1046A-

TSN

LS1046A

Description

Pin

Name

Signal

Pin

Name

1,8V

G5

LOCK

Lock

1,8V

C8

RY/BY

→

IFC-RB0#

→

C16

IFC_RB0#

ready/busy,

4,7K pullup

1,8V

D4

RE#

←

IFC-OE#

←

C18

IFC_OE#

read enable

1,8V

C6

CE#

←

IFC-CS0#

←

C17

IFC_CS0#

chip select

1,8V

D3,G4,H8,

J6

VCC

+1.8V

C5,F7,K3,

K8

GND

GND

1,8V

D5

CLE

←

IFC-CLE

←

C19

IFC_CLE

command

latch enable

1,8V

C4

ALE

←

IFC-AVD

←

A18

IFC_AVD

address latch

enable

1,8V

C7

WE#

←

IFC-WE#

←

C15

IFC_WE0#

write enable

1,8V

C3

WP#

←

IFC-WP#

←

D19

IFC_WP0#

write protect

1,8V

H4

D0

↔

IFC-AD7

↔

B12

IFC_AD7

data line

1,8V

J4

D1

↔

IFC-AD6

↔

A11

IFC_AD6

data line

1,8V

K4

D2

↔

IFC-AD5

↔

B11

IFC_AD5

data line

1,8V

K5

D3

↔

IFC-AD4

↔

A10

IFC_AD4

data line

1,8V

K6

D4

↔

IFC-AD3

↔

A9

IFC_AD3

data line

1,8V

J7

D5

↔

IFC-AD2

↔

B9

IFC_AD2

data line

1,8V

K7

D6

↔

IFC-AD1

↔

A8

IFC_AD1

data line

1,8V

J8

D7

↔

IFC-AD0

↔

B8

IFC_AD0

data line

G3

n.c.

Not connect

G8

n.c.

Not connect

Table 5-5 NAND Flash pin assignments