System Core, Boot Configuration and On-Board Memory 5

miriac SBC-LS1046A-TSN_User Manual

V 2.0

32/68

© MicroSys Electronics GmbH 20178

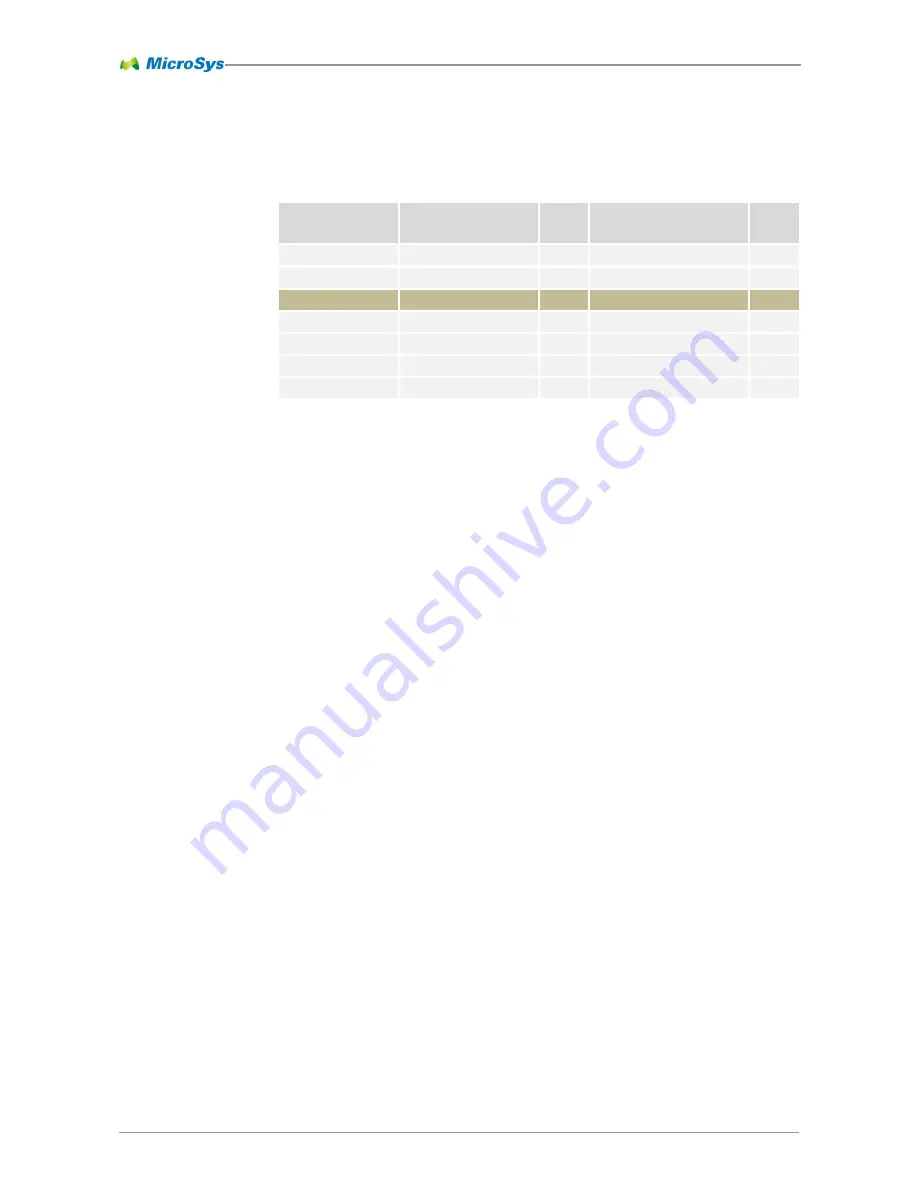

The I²C bus 2 has the following layout:

I/O Range: LVTTL

Device

SCL

(Signal Name)

Pin

SDA

(Signal Name)

Pin

LS1046A

IIC2_SCL

K3

IIC2_SDA

L3

↓

↕

Module Connector

I2C2_SCL

B75

I2C2_SDA

B74

↓

↕

MAX9611AUB

SCL

6

SDA

7

↓

↕

PCA9517ADP

SCL

2

SDA

3

Table 5-10 I²C-2 pin assignment