9-2

9.1 Overview

9.1

Overview

The multiple CPU high speed transmission dedicated instruction is an instruction used to read

and write device data between the multiple Universal model QCPUs.

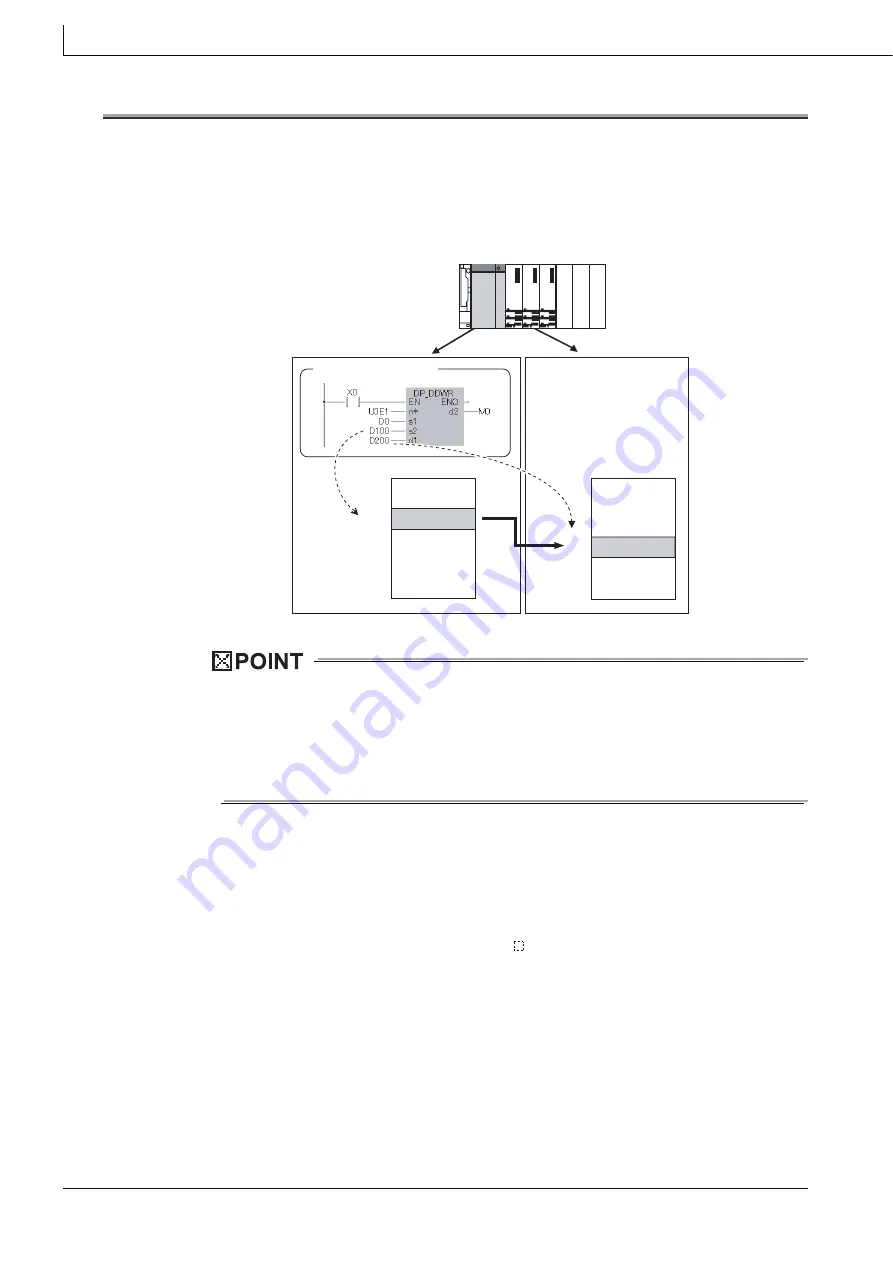

The following figure shows the operation when the data are read from the CPU No. 1 and written

to the CPU No. 2 using the multiple CPU high speed transmission dedicated instruction.

This instruction can be used for the following CPU modules only, including the

ones used as host CPU and other CPU (target CPU for instruction execution).

• Q3UDCPU, Q4UDHCPU, Q06UDHCPU, Q13UDHCPU or Q26UDHCPU with a

serial number whose first five digits are '10012' or higher

• QnUDE(H)CPU

(1) System configuration and parameter settings for executing the multiple CPU high speed

transmission dedicated instruction

This instruction can be executed under the following system configuration and parameter

settings.

• QnUD(H)CPU or QnUDE(H)CPU is used for the CPU No. 1.

• Multiple CPU high speed main base unit (Q3 DB) is used.

• "Multiple CPU High Speed Transmission Area Setting is valid." is selected in the multiple

CPU setting of the PLC parameter.

CPU No. 1

CPU No. 2

D0

D100

Data write

D0

D200

User program

Summary of Contents for MELSEC Q Series

Page 1: ...Structured Programming Manual Mitsubishi Programmable Controller QCPU Common Instructions ...

Page 2: ......

Page 14: ...A 12 MEMO ...

Page 340: ...6 178 MEMO MTR ...

Page 708: ...7 368 MEMO ...

Page 776: ...8 68 MEMO ...

Page 796: ...9 20 MEMO ...

Page 804: ...App 8 MEMO ...

Page 812: ...Index 8 MEMO ...

Page 815: ......