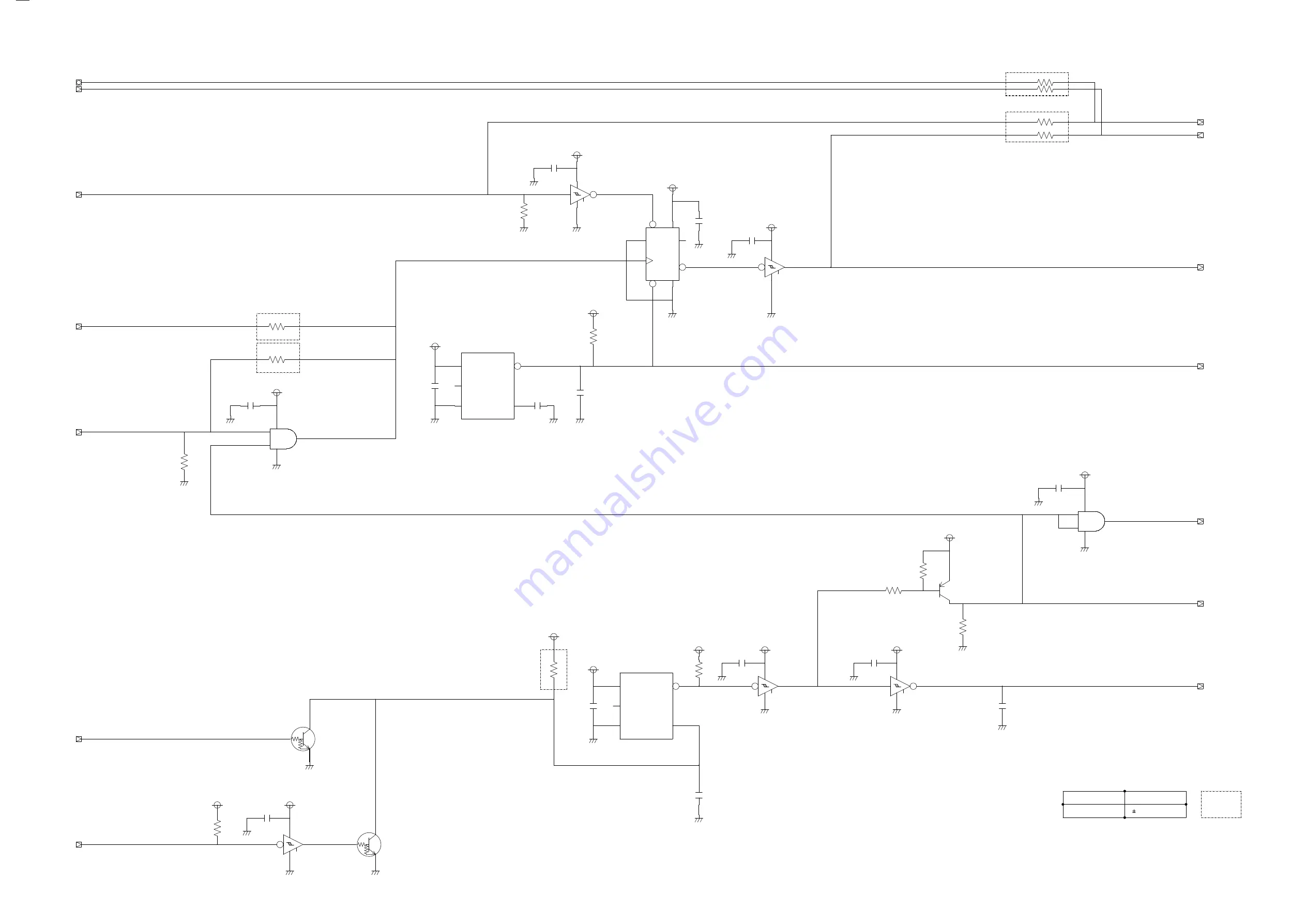

OPEN

B

5%,1/16W

RESISTOR

UNLESS_OTHERWISE

CAPACITOR

RESET_DDR2*

TC7SG08FU(T5LMBS_F

GND1

0.1u

4

GND1

14G1>

15F6>

14E5<

14E5>

4C2>

12B9<

4C2<>

12B9<>

4F2<

11G2<

3F9<

9C2<

3G2<

12E4<

3B9>

4F2>

4E9>

NJ3P_SCIF_TX2

NJ3_SCL2

NJ3_SDA2

MBKPRST*

MASK_RST*

NJ3_PRESET*

NJ3P_SDSELF

CKE_SUB

10V

C2D3

0.1u

GND1

R2

C6

10k

+3.3V

+3.3V

+3.3V

OPEN

100k

R2

C5

C2

D0

0.1u 16V

GND1

4

2

3

1

PST3628NR

NC

VCC

VOUT

IC2C7

GND

GND1

GND1

E

B

C

DTC124EU

GND1

DTC124EU

E

C

+3.3V

C2D5

0.1u

10V

GND1

+3.3V

10k

R2

C4

TC7SH14FU

IC2C5

3

NC

GND

VCC

2

5

1

4

GND1

0

OPEN

R2D7

0

OPEN

R2D6

0

R2D4

OPEN

0

R2D5

OPEN

+3.3VB

C2C0

10V

0.1u

+1.8VB

4

2

3

GND

VCC

1

5

IC2D0

GND1

GND1

+3.3V

1k

R2C9

GND1

C

B

2SA1576AR_S

E

Q2C2

R2

C8

4.7k

R2C7

+3.3V

VCC

5

IC2C9

3

GND

NC

1

2

4

TC7SH14FU

GND1

C2

D2

+3.3V

10V

NC

VCC

GND1

+3.3VB

GND1

7

VCC

CLR*

D

Q

4

2

1

3

PRE*

Q*

GND

CLK

IC2C1

GND1

C2D4

0.1u

10V

GND1

+3.3V

TC7SH14FU

1

GND

5

3

NC

4

VCC

IC2C8

2

GND1

TC7SH14FU

1

3

NC

5

GND

VCC

2

IC2C0

R2

C0

10k

+3.3VB

GND1

C2C5

+3.3VB

GND

3

1

5

4

2

PST3623NR

VCC

CD

IC2C3

VOUT

GND1

GND1

OPEN

0

R2C1

0

OPEN

R2C2

+3.3VB

C2C3

0.1u

10V

GND1

GND1

4

GND

3

VCC

1

5

2

IC2C4

TC7SH08FU

2.2k

R2

D1

C2C2

10V

0.1u

5

C2

C1

8

2

4

1

5

3

12k

GND1

NJ3P_SDBUP

NJ3P_SCIF_RX2

GND1

D2SD_CKE2

1000p

GND1

B

Q2C0

Q2C1

10k

R2

C3

C2

C4

0.1u 10V

NC

C2

C6

100p (CH)

GND

TC7SH14FU

C2D1

0.1u

10V

(CH)

50V

100p

GND1

5

CD

10V

0.1u

C2

C9

NJ3_DEBUG_E10A_RST*

MAIN_RESETIN

6

TC7WH74FU-TE12L

IC2C2

91

Copyright (C) Mitsubishi Electric Corporation. Your company internal use only.

SCHEMATIC DIAGRAM NJ3MP2(DIGITAL) RESET,DDR2-BACKUP MODEL : NR-242UM-13LND0,13-WS