MOTOROLA CMOS LOGIC DATA

MC14490

6–210

Hex Contact Bounce Eliminator

The MC14490 is constructed with complementary MOS enhancement

mode devices, and is used for the elimination of extraneous level changes

that result when interfacing with mechanical contacts. The digital contact

bounce eliminator circuit takes an input signal from a bouncing contact and

generates a clean digital signal four clock periods after the input has

stabilized. The bounce eliminator circuit will remove bounce on both the

“make” and the “break” of a contact closure. The clock for operation of the

MC14490 is derived from an internal R–C oscillator which requires only an

external capacitor to adjust for the desired operating frequency (bounce

delay). The clock may also be driven from an external clock source or the

oscillator of another MC14490 (see Figure 5).

NOTE: Immediately after power–up, the outputs of the MC14490 are in

indeterminate states.

•

Diode Protection on All Inputs

•

Six Debouncers Per Package

•

Internal Pullups on All Data Inputs

•

Can Be Used as a Digital Integrator, System Synchronizer, or Delay

Line

•

Internal Oscillator (R–C), or External Clock Source

•

TTL Compatible Data Inputs/Outputs

•

Single Line Input, Debounces Both “Make” and “Break” Contacts

•

Does Not Require “Form C” (Single Pole Double Throw) Input Signal

•

Cascadable for Longer Time Delays

•

Schmitt Trigger on Clock Input (Pin 7)

•

Supply Voltage Range = 3.0 V to 18 V

•

Chip Complexity: 546 FETs or 136.5 Equivalent Gates

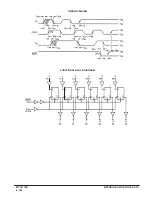

BLOCK DIAGRAM

Ain 1

OSCin 7

OSCout 9

Bin 14

Cin 3

Din 12

Ein 5

Fin 10

+VDD

φ

1

φ

2

OSCILLATOR

AND

TWO–PHASE

CLOCK GENERATOR

DATA

SHIFT

LOAD

4–BIT STATIC SHIFT REGISTER

1/2–BIT

DELAY

φ

1

φ

2

φ

1

φ

2

15 Aout

VDD = PIN 16

VSS = PIN 8

φ

1

φ

2

φ

1

φ

2

φ

1

φ

2

φ

1

φ

2

φ

1

φ

2

2 Bout

13 Cout

4 Dout

11 Eout

6 Fout

IDENTICAL TO ABOVE STAGE

IDENTICAL TO ABOVE STAGE

IDENTICAL TO ABOVE STAGE

IDENTICAL TO ABOVE STAGE

IDENTICAL TO ABOVE STAGE

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

MC14490

L SUFFIX

CERAMIC

CASE 620

P SUFFIX

PLASTIC

CASE 648

DW SUFFIX

SOIC

CASE 751G

ORDERING INFORMATION

MC14490P

Plastic

MC14490L

Ceramic

MC14490DW

SOIC

TA = – 55

°

to 125

°

C for all packages.

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......