MOTOROLA CMOS LOGIC DATA

MC14510B

6–250

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ

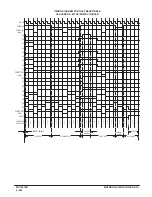

SWITCHING CHARACTERISTICS*

(CL = 50 pF, TA = 25

_

C, See Figure 2)

All Types

Characteristic

Symbol

VDD

Min

Typ #

Max

Unit

Output Rise and Fall Time

tTLH, tTHL = (1.5 ns/pF) CL + 25 ns

tTLH, tTHL = (0.75 ns/pF) CL + 12.5 ns

tTLH, tTHL = (0.55 ns/pF) CL + 9.5 ns

tTLH,

tTHL

5.0

10

15

—

—

—

100

50

40

200

100

80

ns

Propagation Delay Time

Clock to Q

tPLH, tPHL = (1.7 ns/pF) CL + 230 ns

tPLH, tPHL = (0.66 ns/pF) CL + 97 ns

tPLH, tPHL = (0.5 ns/pF) CL + 75 ns

tPLH,

tPHL

5.0

10

15

—

—

—

315

130

100

630

260

200

ns

Clock to Carry Out

tPLH, tPHL = (1.7 ns/pF) CL + 230 ns

tPLH, tPHL = (0.66 ns/pF) CL + 97 ns

tPLH, tPHL = (0.5 ns/pF) CL + 75 ns

tPLH,

tPHL

5.0

10

15

—

—

—

315

130

100

630

260

200

ns

Carry In to Carry Out

tPLH, tPHL = (1.7 ns/pF) CL + 230 ns

tPLH, tPHL = (0.66 ns/pF) CL + 47 ns

tPLH, tPHL = (0.5 ns/pF) CL + 35 ns

tPLH,

tPHL

5.0

10

15

—

—

—

180

80

60

360

160

120

ns

Preset or Reset to Q

tPLH, tPHL = (1.7 ns/pF) CL + 230 ns

tPLH, tPHL = (0.66 ns/pF) CL + 97 ns

tPLH, tPHL = (0.5 ns/pF) CL + 75 ns

tPLH,

tPHL

5.0

10

15

—

—

—

315

130

100

630

260

200

ns

Preset or Reset to Carry Out

tPLH, tPHL = (1.7 ns/pF) CL + 465 ns

tPLH, tPHL = (0.66 ns/pF) CL + 192 ns

tPLH, tPHL = (0.5 ns/pF) CL + 125 ns

tPLH,

tPHL

5.0

10

15

—

—

—

550

225

150

1100

450

300

ns

Reset Pulse Width

tw(H)

5.0

10

15

360

210

160

180

105

80

—

—

—

ns

Clock Pulse Width

tw(H)

5.0

10

15

350

170

140

200

100

75

—

—

—

ns

Clock Pulse Frequency

fcl

5.0

10

15

—

—

—

3.0

6.0

8.0

1.5

3.0

4.0

MHz

Preset or Reset Removal Time

The Preset or Reset Signal must be low prior to a

positive–going transition of the clock.

trem

5.0

10

15

650

230

180

325

115

90

—

—

—

ns

Clock Rise and Fall Time

tTLH,

tTHL

5.0

10

15

—

—

—

—

—

—

15

5

4

µ

s

Setup Time

Carry In to Clock

tsu

5.0

10

15

260

120

100

130

60

50

—

—

—

ns

Hold Time

Clock to Carry In

th

5.0

10

15

0

10

10

– 50

– 15

– 5

—

—

—

ns

Setup Time

Up/Down to Clock

tsu

5.0

10

15

500

200

175

250

100

75

—

—

—

ns

Hold Time

Clock to Up/Down

th

5.0

10

15

– 70

– 30

– 20

– 140

– 80

– 50

—

—

—

ns

Setup Time

Pn to PE

tsu

5.0

10

15

– 50

– 30

– 25

– 100

– 65

– 55

—

—

—

ns

Hold Time

PE to Pn

th

5.0

10

15

480

410

410

240

205

205

—

—

—

ns

Preset Enable Pulse Width

tWH

5.0

10

15

200

100

80

100

50

40

—

—

—

ns

* The formulas given are for the typical characteristics only at 25

_

C.

#Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......