MOTOROLA CMOS LOGIC DATA

MC14522B MC14526B

6–310

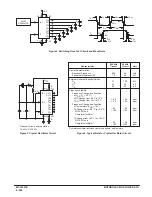

Figure 1. Typical Output Source

Characteristics Test Circuit

Figure 2. Typical Output Sink

Characteristics Test Circuit

CF

PE

P0

P1

P2

P3

RESET

INHIBIT

CLOCK

Q0

Q1

Q2

Q3

“0”

VSS

VDD = –VGS

VOH

IOH

EXTERNAL

POWER

SUPPLY

CF

PE

P0

P1

P2

P3

RESET

INHIBIT

CLOCK

Q0

Q1

Q2

Q3

“0”

VSS

VDD = VGS

VOL

IOL

EXTERNAL

POWER

SUPPLY

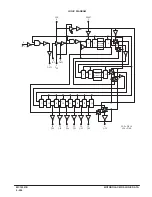

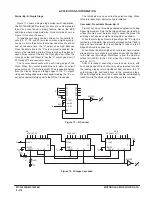

Figure 3. Power Dissipation

Figure 4. Test Circuit

CF

PE

P0

P1

P2

P3

RESET

INHIBIT

CLOCK

Q0

Q1

Q2

Q3

“0”

VSS

VDD

CL

CL

CL

CL

CL

PULSE

GENERATOR

20 ns

20 ns

CLOCK

90%

10%

50%

VARIABLE

WIDTH

50% DUTY CYCLE

VSS

VDD

DEVICE

UNDER

TEST

TEST POINT

Q or “0”

CL*

* Includes all probe and jig capacitance.

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......