MOTOROLA CMOS LOGIC DATA

MC14539B

6–376

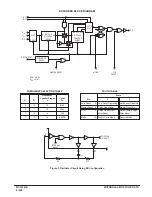

Figure 2. Power Dissipation Test Circuit and Waveform

PULSE

GENERATOR

VDD

VSS

A

B

ST

X0

X1

X2

X3

ST

′

Y0

Y1

Y2

Y3

W

Z

20 ns

20 ns

Vin

VDD

CL

CL

0.01

µ

F

CERAMIC

500

µ

F

VSS

90%

50%

10%

50% DUTY CYCLE

ID

PIN ASSIGNMENT

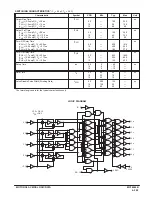

LOGIC DIAGRAM

13

14

15

16

9

10

11

12

5

4

3

2

1

8

7

6

Y2

Y3

A

ST

′

VDD

W

Y0

Y1

X2

X3

B

ST

VSS

Z

X0

X1

B

A

X0

X1

X2

X3

Y0

Y1

Y2

Y3

2

14

6

5

4

3

10

11

12

13

ST

1

Z

7

9

W

15

ST

′

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......