MOTOROLA CMOS LOGIC DATA

6–439

MC14560B

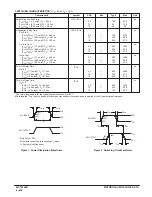

Table 1. Sum = A + B + C

Binary Sums

Decimal

Numbers

Corrected

Binary Sums

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

Non valid

1101

BCD

1110

representation

1111

0000 + Carry

0001 + Carry

0010 + Carry

0011 + Carry

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

0000 + Carry

0001 + Carry

0010 + Carry

0011 + Carry

0100 + Carry

0101 + Carry

0110 + Carry

0111 + Carry

1000 + Carry

1001 + Carry

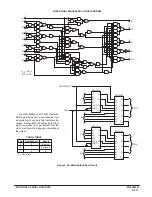

ADDITION AND SUBTRACTION OF SIGNED NBCD

NUMBERS

Using MC14560 NBCD Adders and MC14561 9’s Comple-

menters, a sign and magnitude adder/subtracter can be con-

figured (Figure 5). Inputs A and B are signed positive (AS, BS

= “0”) or negative (AS, BS = “1”). B is added to or subtracted

from A under control of an Add/Sub line (subtraction = “1”).

The result, R, of the operation is positive signed, positive

signed with overflow, negative signed, or negative signed

with overflow. Add/subtract time is typically 0.6 + 0.4n

µ

s for

n decades.

An exclusive–OR of Add/Sub line and BS produces B

′

,

which controls the B complementers. If BS, the sign of B, is a

logical “1” (B is negative) and the Add/Sub line is a “0” (add

B to A), then the output of the exclusive–OR (BS

′

) is a logical

“1” and B is complemented. If BS = “1” and Add/Sub = “1”, B

is not complemented since subtracting a negative number is

the same as adding a positive number. When Add/Sub is a

“1” and BS = “0”, BS

′

is a “1” and B is complemented. The A

complementer is controlled by the A sign bit, AS. When AS =

“1”, A is complemented.

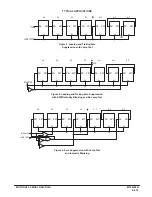

Figure 4. Unsigned NBCD Addition Algorithm

6,941

5,870

+

4 BIT BINARY FULL ADDER

DIGIT BINARY SUMS

BINARY SUMS WITH

CARRY FROM CONVERTERS

CODE CONVERTERS

CORRECTED SUM

12,811

A

B

Cin

Cout

BINARY TO NBCD

CODE CONVERTER

RESULT, R

A1

B1

A2

B2

An

Bn

Cin

Cin

Cin

Cout

Cout

Cout

R1

R2

Rn

OVERFLOW

THOUSANDS

0110

0101

HUNDREDS

1001

1000

TENS

0100

0111

UNITS

0001

0000

ADDER

Cin

ADDER

Cin

ADDER

Cin

ADDER

1

1

0

1011

0001

1011

0001

1

1100

0010

1011

0001

1

Cout

Cout

Cout

Cout

1

0 0 1 0

1 0 0 0

0 0 0 1

0 0 0 1

Figure 5. Addition of Unsigned NBCD Numbers

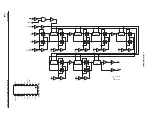

(a) MC14560 Block Diagram

(b) n–Decade Adder

Typical Add Time = 0.1 + 0.2n

µ

s

where n = Number of Decades

4 BIT BINARY ADDERS

MC14560

MC14560

MC14560

Summary of Contents for CMOS Logic

Page 1: ......

Page 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Page 6: ...Master Index 1 ...

Page 12: ...Product Selection Guide 2 ...

Page 17: ...The Better Program 3 ...

Page 20: ...B and UB Series Family Data 4 ...

Page 25: ...CMOS Handling and Design Guidelines 5 ...

Page 32: ...CMOS Handling and Design Guidelines 5 ...

Page 39: ...Data Sheets 6 ...

Page 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Page 555: ...CMOS Reliability 7 ...

Page 561: ...Equivalent Gate Count 8 ...

Page 563: ...Packaging Information Including Surface Mounts 9 ...

Page 571: ......