4-1

4

4

Functional Description

Introduction

The CPIP5430 series products include the following features. The

processor(s) are socketed PGA devices. The amount of memory available

and the availability of the PMC slots vary, based on the specific model. The

Hard Disk Drive (HDD), if installed, occupies one PMC site. The Rear

Transition Module, CPIP5430-RTM1, is an optional item.

The following table lists the features of the CPIP5430.

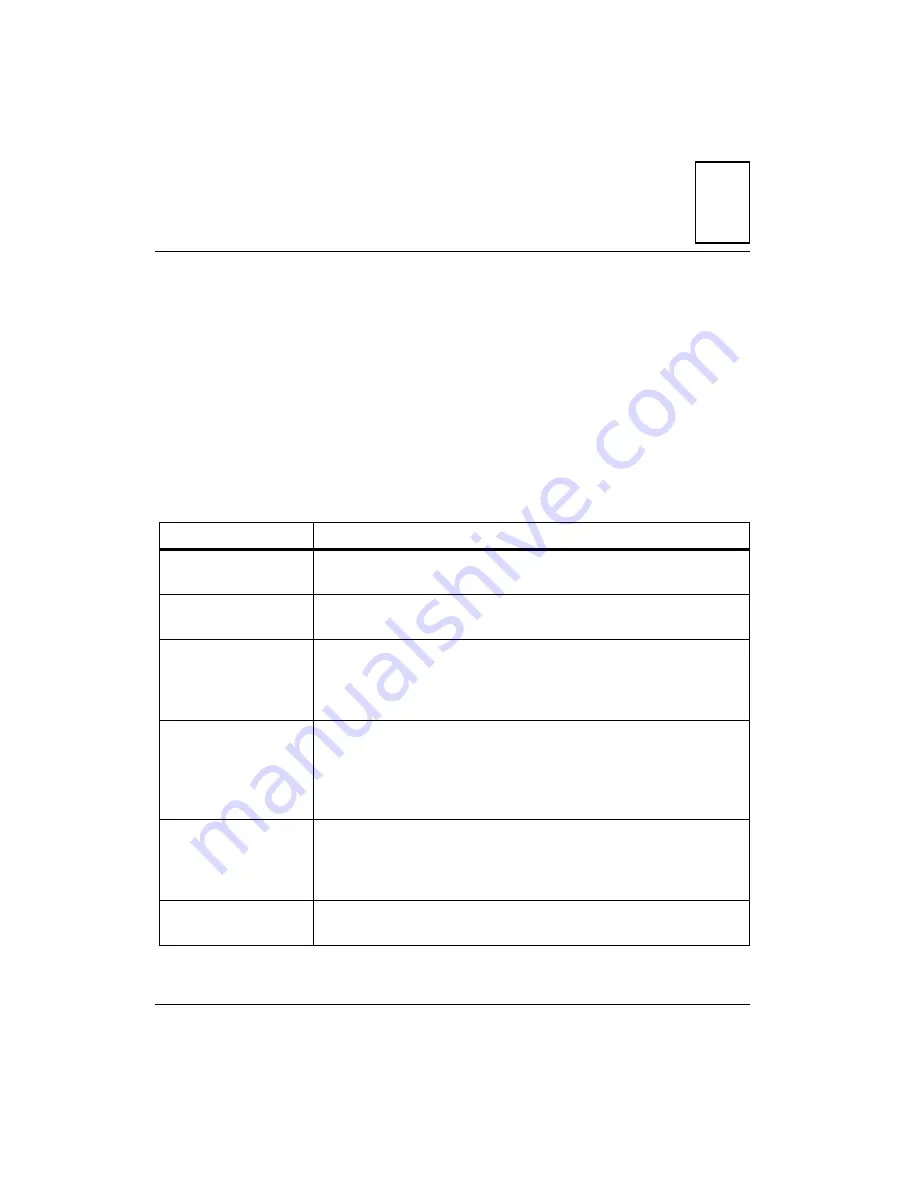

Table 4-1. CPIP5430 Features Summary

Feature

Description

Form Factor

6U board (233.35, +0.0/-0.3mm x 160.0, +0.0/-0.3mm) 1-slot width

Supports rear I/O through J3 and J5

CPU/Cache

Supports Intel Mobile Pentium 4 Processor-M processor with 512KB

on-die L2 cache at full core speed and 400 MHz FSB

Chipset

Intel 875P MCH with 6300 ESB ICH

Supports up to 4GB of DDR memory

Supports ECC, on-memory bus

64-bit, 33/66 MHz, on board, PCI bus interface

System Memory

Supports 266 MHz to 400 MHz DDR

Supports two onboard SO-DIMM sockets

Supports memory size up to 4GB

Supports 144-pin registered SO-DIMMs

ECC supported

IDE Port

Supports one (secondary) EIDE channel through J5 rear I/O for up to

two IDE devices

An onboard 44-pin IDE pin header for optional 2.5" hard drive or Disk-

on-Module on front controller (primary channel).

On-Board Super I/O

The function of the SIO is to provide legacy serial port controller

functionality (16550 compatible).