MOTOROLA

INSTRUCTION REFERENCE

CPU12

A-24

REFERENCE MANUAL

Key to

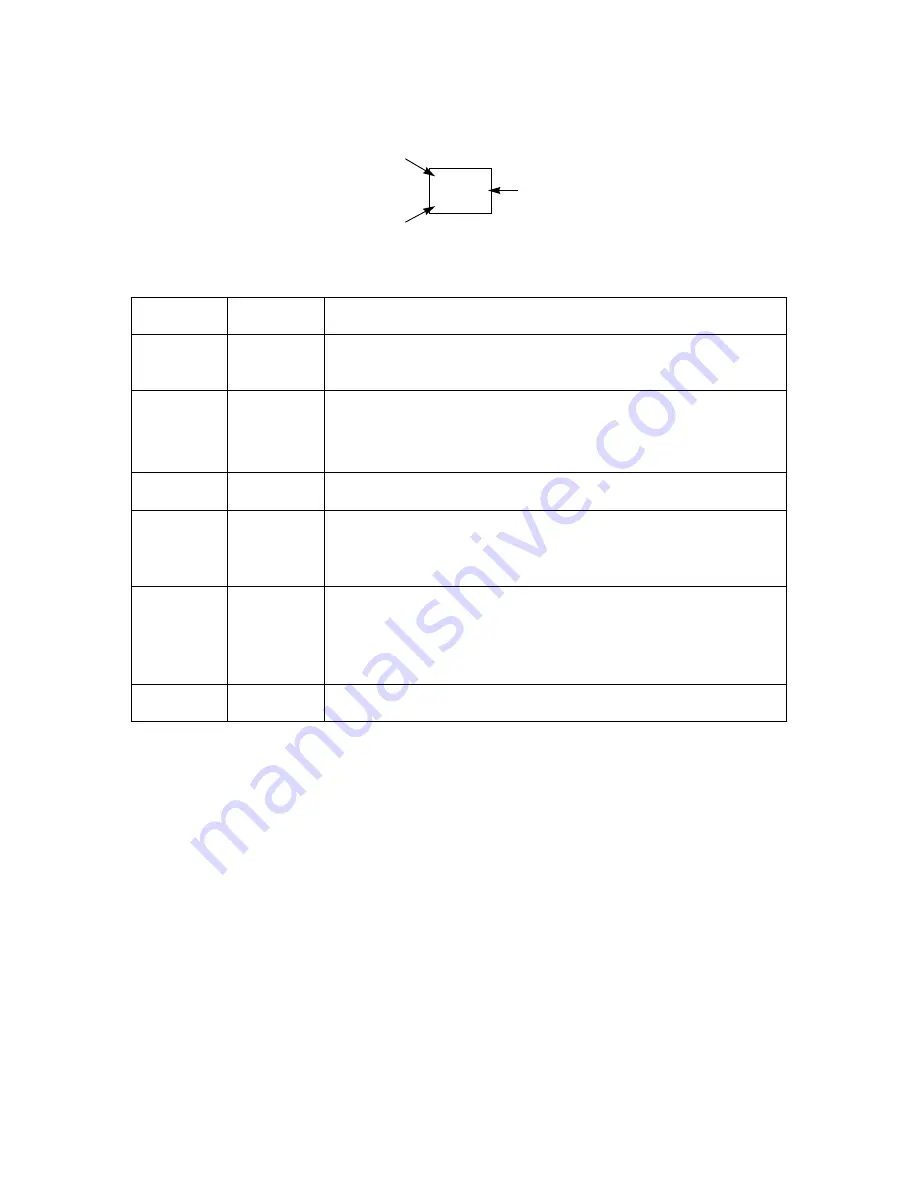

Table A-5 Indexed Addressing Mode Summary

Postbyte

Code (xb)

Operand

Syntax

Comments

rr0nnnnn

,r

n,r

–n,r

5-bit constant offset

n = –16 to +15

rr can specify X, Y, SP, or PC

111rr0zs

n,r

–n,r

Constant offset (9- or 16-bit signed)

z-

0 = 9-bit with sign in LSB of postbyte (s)

1 = 16-bit

if z = s = 1, 16-bit offset indexed-indirect (see below)

rr can specify X, Y, SP, or PC

111rr011

[n,r]

16-bit offset indexed-indirect

rr can specify X, Y, SP, or PC

rr1pnnnn

n,–r

n,+r

n,r–

n,r+

Auto pre-decrement /increment or Auto post-decrement/increment;

p = pre-(0) or post-(1), n = –8 to –1, +1 to +8

rr can specify X, Y, or SP (PC not a valid choice)

111rr1aa

A,r

B,r

D,r

Accumulator offset (unsigned 8-bit or 16-bit)

aa - 00 = A

01 = B

10 = D (16-bit)

11 = see accumulator D offset indexed-indirect

rr can specify X, Y, SP, or PC

111rr111

[D,r]

Accumulator D offset indexed-indirect

rr can specify X, Y, SP, or PC

postbyte (hex)

B0

#,REG

type

type offset used

source code syntax

Summary of Contents for CPU12

Page 8: ...MOTOROLA CPU12 viii REFERENCE MANUAL ...

Page 14: ...MOTOROLA INTRODUCTION CPU12 1 4 REFERENCE MANUAL ...

Page 20: ...MOTOROLA OVERVIEW CPU12 2 6 REFERENCE MANUAL ...

Page 38: ...MOTOROLA INSTRUCTION QUEUE CPU12 4 6 REFERENCE MANUAL ...

Page 300: ...MOTOROLA DEVELOPMENT AND DEBUG SUPPORT CPU12 8 16 REFERENCE MANUAL ...

Page 338: ...MOTOROLA MEMORY EXPANSION CPU12 10 8 REFERENCE MANUAL ...

Page 364: ...MOTOROLA INSTRUCTION REFERENCE CPU12 A 26 REFERENCE MANUAL ...

Page 386: ...MOTOROLA HIGH LEVEL LANGUAGE SUPPORT CPU12 C 6 REFERENCE MANUAL ...

Page 438: ...MOTOROLA SUMMARY OF CHANGES CPU12 S 2 REFERENCE MANUAL ...

Page 439: ......