MOTOROLA

M68HC11 TO M68HC12 UPGRADE PATH

CPU12

B-16

REFERENCE MANUAL

B.7.11 Support for Memory Expansion

Bank switching is a common method of expanding memory beyond the 64-Kbyte limit

of a CPU with a 64-Kbyte address space, but there are some known difficulties asso-

ciated with bank switching. One problem is that interrupts cannot take place during

the bank switching operation. This increases worst case interrupt latency and re-

quires extra programming space and execution time.

Some M68HC12 variants include a built-in bank switching scheme that eliminates

many of the problems associated with external switching logic. The CPU12 includes

CALL and return from call (RTC) instructions that manage the interface to the bank-

switching system. These instructions are analogous to the JSR and RTS instructions,

except that the bank page number is saved and restored automatically during execu-

tion. Since the page change operation is part of an uninterruptable instruction, many

of the difficulties associated with bank switching are eliminated. On M68HC12 deriva-

tives with expanded memory capability, bank numbers are specified by on-chip con-

trol registers. Since the addresses of these control registers may not be the same in

all M68HC12 derivatives, the CPU12 has a dedicated control line to the on-chip inte-

gration module that indicates when a memory-expansion register is being read or

written. This allows the CPU to access the PPAGE register without knowing the regis-

ter address.

The indexed indirect versions of the CALL instruction access the address of the

called routine and the destination page value indirectly. For other addressing mode

variations of the CALL instruction, the destination page value is provided as immedi-

ate data in the instruction object code. CALL and RTC execute correctly in the normal

64-Kbyte address space, thus providing for portable code.

Summary of Contents for CPU12

Page 8: ...MOTOROLA CPU12 viii REFERENCE MANUAL ...

Page 14: ...MOTOROLA INTRODUCTION CPU12 1 4 REFERENCE MANUAL ...

Page 20: ...MOTOROLA OVERVIEW CPU12 2 6 REFERENCE MANUAL ...

Page 38: ...MOTOROLA INSTRUCTION QUEUE CPU12 4 6 REFERENCE MANUAL ...

Page 300: ...MOTOROLA DEVELOPMENT AND DEBUG SUPPORT CPU12 8 16 REFERENCE MANUAL ...

Page 338: ...MOTOROLA MEMORY EXPANSION CPU12 10 8 REFERENCE MANUAL ...

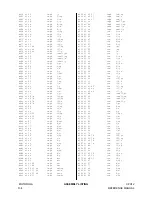

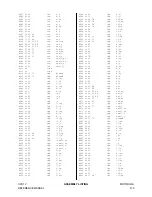

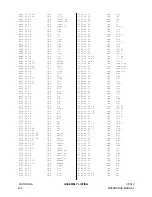

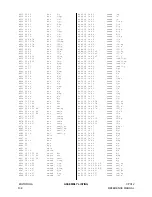

Page 364: ...MOTOROLA INSTRUCTION REFERENCE CPU12 A 26 REFERENCE MANUAL ...

Page 386: ...MOTOROLA HIGH LEVEL LANGUAGE SUPPORT CPU12 C 6 REFERENCE MANUAL ...

Page 438: ...MOTOROLA SUMMARY OF CHANGES CPU12 S 2 REFERENCE MANUAL ...

Page 439: ......