CPU12

INSTRUCTION GLOSSARY

MOTOROLA

REFERENCE MANUAL

6-9

Operation:

(B)

+

(X)

⇒

X

Description:

Adds the 8-bit unsigned content of accumulator B to the content of index

register X considering the possible carry out of the low-order byte of X;

places the result in X. The content of B is not changed.

This mnemonic is implemented by the LEAX B,X instruction. The LEAX

instruction allows A, B, D, or a constant to be added to X. For compati-

bility with the M68HC11, the mnemonic ABX is translated into the LEAX

B,X instruction by the assembler.

Condition Codes and Boolean Formulas:

None affected.

Addressing Modes, Machine Code, and Execution Times:

ABX

Add Accumulator B to

Index Register X

ABX

S

X

H

I

N

Z

V

C

–

–

–

–

–

–

–

–

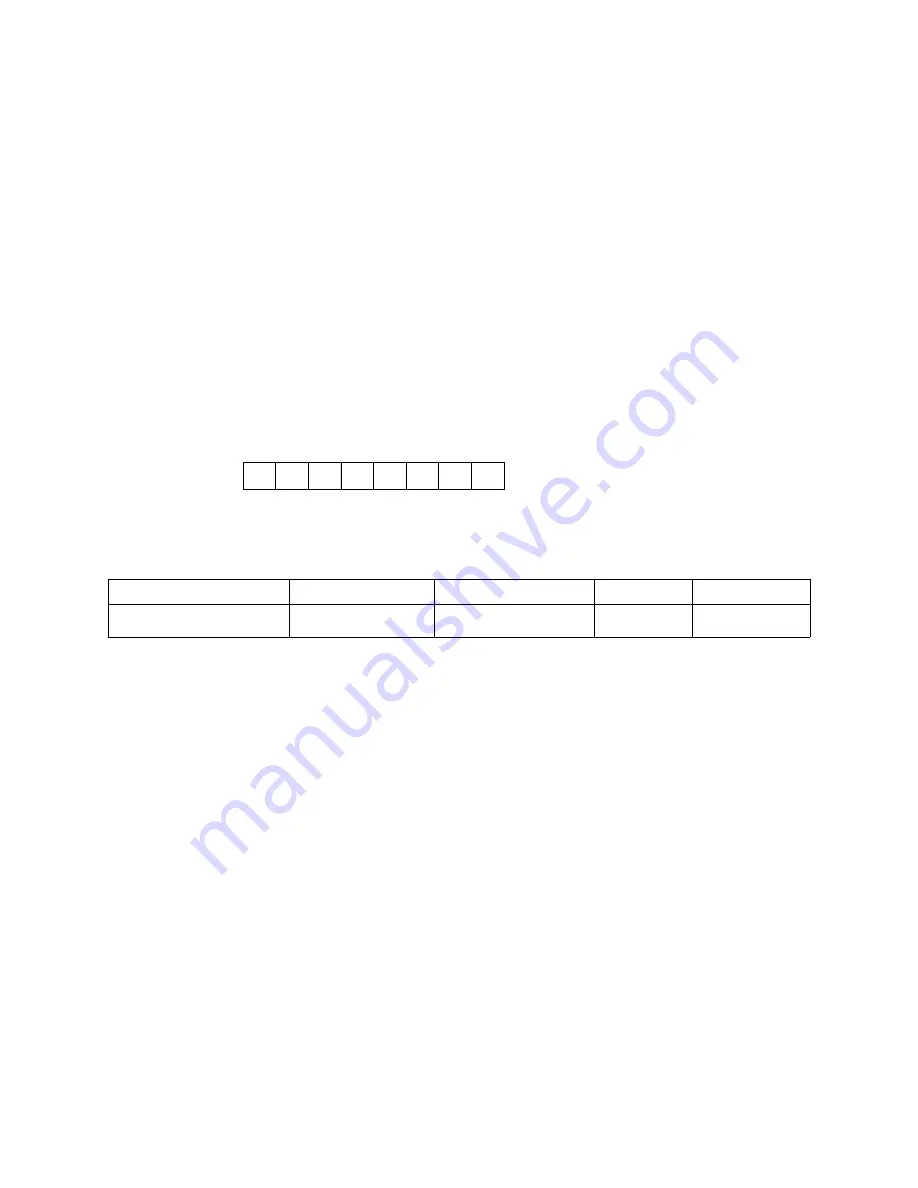

Source Form

Address Mode

Object Code

Cycles

Access Detail

ABX

translates to...

LEAX B,X

IDX

1A E5

2

PP

1

Notes:

1. Due to internal CPU requirements, the program word fetch is performed twice to the same address during this

instruction.

Summary of Contents for CPU12

Page 8: ...MOTOROLA CPU12 viii REFERENCE MANUAL ...

Page 14: ...MOTOROLA INTRODUCTION CPU12 1 4 REFERENCE MANUAL ...

Page 20: ...MOTOROLA OVERVIEW CPU12 2 6 REFERENCE MANUAL ...

Page 38: ...MOTOROLA INSTRUCTION QUEUE CPU12 4 6 REFERENCE MANUAL ...

Page 300: ...MOTOROLA DEVELOPMENT AND DEBUG SUPPORT CPU12 8 16 REFERENCE MANUAL ...

Page 338: ...MOTOROLA MEMORY EXPANSION CPU12 10 8 REFERENCE MANUAL ...

Page 364: ...MOTOROLA INSTRUCTION REFERENCE CPU12 A 26 REFERENCE MANUAL ...

Page 386: ...MOTOROLA HIGH LEVEL LANGUAGE SUPPORT CPU12 C 6 REFERENCE MANUAL ...

Page 438: ...MOTOROLA SUMMARY OF CHANGES CPU12 S 2 REFERENCE MANUAL ...

Page 439: ......