1-8

System Bus, HDI16, and Interrupt Signals

1.5 System Bus, HDI16, and Interrupt Signals

The system bus, HDI16, and interrupt signals are grouped together because they use a common set of

signal lines. Individual assignment of a signal to a specific signal line is configured through registers in

the System Interface Unit (SIU) and the Host Interface (HDI16). Table 1-4 describes the signals in this

group.

Note:

To boot from the host interface, the HDI16 must be enabled by pulling up the HPE signal line

during

PORESET

. If the HPE signal is pulled up, the configuration word must then be loaded

from the host. The configuration word must set the Internal Space Port Size bit in the Bus

Control Register (BCR[ISPS]) to change the system data bus width from 64 bits to 32 bits and

reassign the upper 32 bits to their HDI16 functions. Never set the Host Port Enable (HEN) bit in

the Host Port Control Register (HPCR) to enable the HDI16, unless the bus size is first changed

from 64 bits to 32 bits by setting the BCR[ISPS] bit. Otherwise, unpredictable operation may

occur.

Although there are eight interrupt request (IRQ) connections to the core processor, there are multiple

external lines that can connect to these internal signal lines. After reset, the default configuration includes

two IRQ1 and two IRQ7 input lines. The designer must select one line for each required interrupt and

reconfigure the other external signal line or lines for alternate functions.

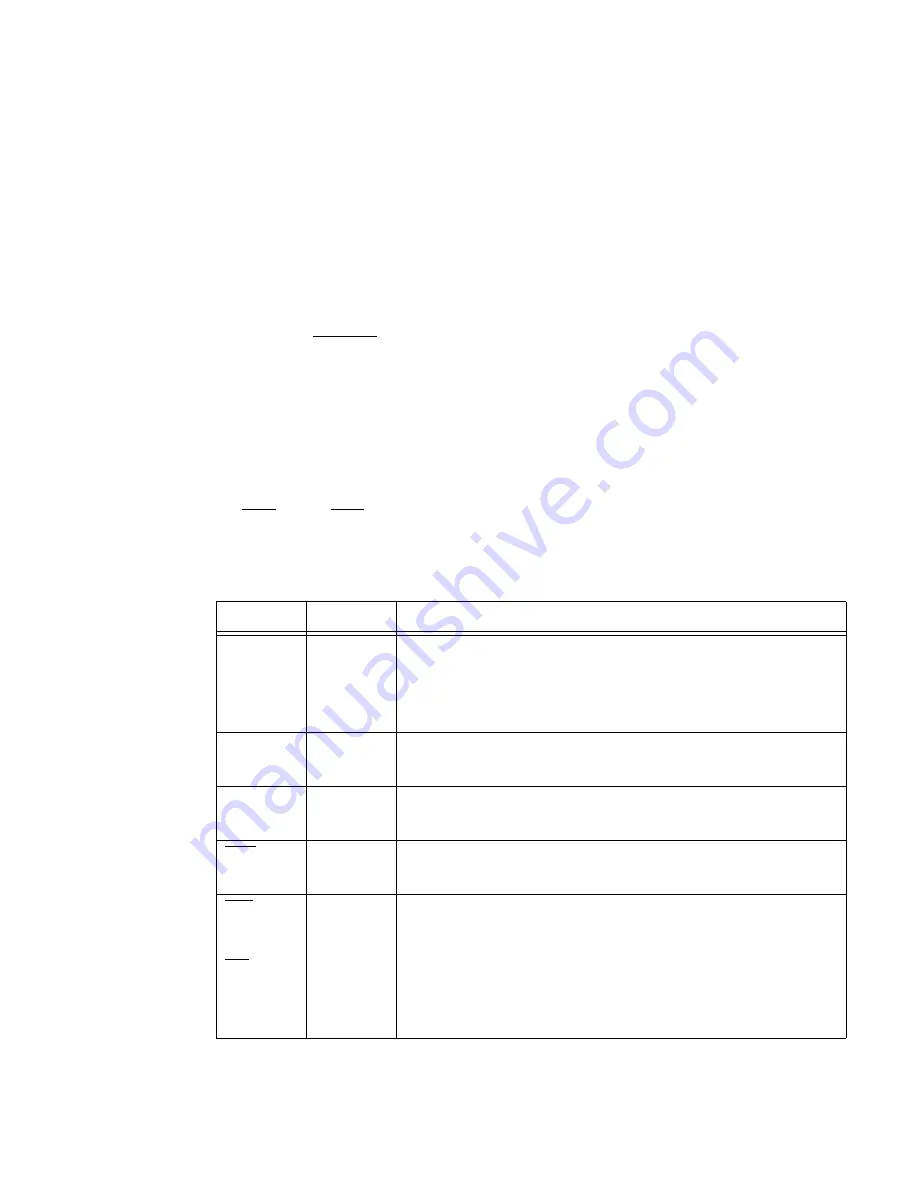

Table 1-4. System Bus, HDI16, and Interrupt Signals

Signal Data

Flow

Description

A[0–31]

Input/Output

Address Bus

When the MSC8101 is in external master bus mode, these pins function as the

address bus. The MSC8101 drives the address of its internal bus masters and

responds to addresses generated by external bus masters. When the MSC8101 is

in Internal Master Bus mode, these pins are used as address lines connected to

memory devices and are controlled by the MSC8101 memory controller.

TT[0–4]

Input/Output

Bus Transfer Type

The bus master drives these pins during the address tenure to specify the type of

transaction.

TSIZ[0–3]

Input/Output

Transfer Size

The bus master drives these pins with a value indicating the number of bytes

transferred in the current transaction.

TBST

Input/Output

Bus Transfer Burst

The bus master asserts this pin to indicate that the current transaction is a burst

transaction (transfers four quad words).

IRQ1

GBL

Input

Input/Output

Interrupt Request 1

1

One of eight external lines that can request a service routine, via the internal

interrupt controller, from the SC140 core.

Global

1

When a master within the chip initiates a bus transaction, it drives this pin. When

an external master initiates a bus transaction, it should drive this pin. Assertion of

this pin indicates that the transfer is global and it should be snooped by caches in

the system.