1-26

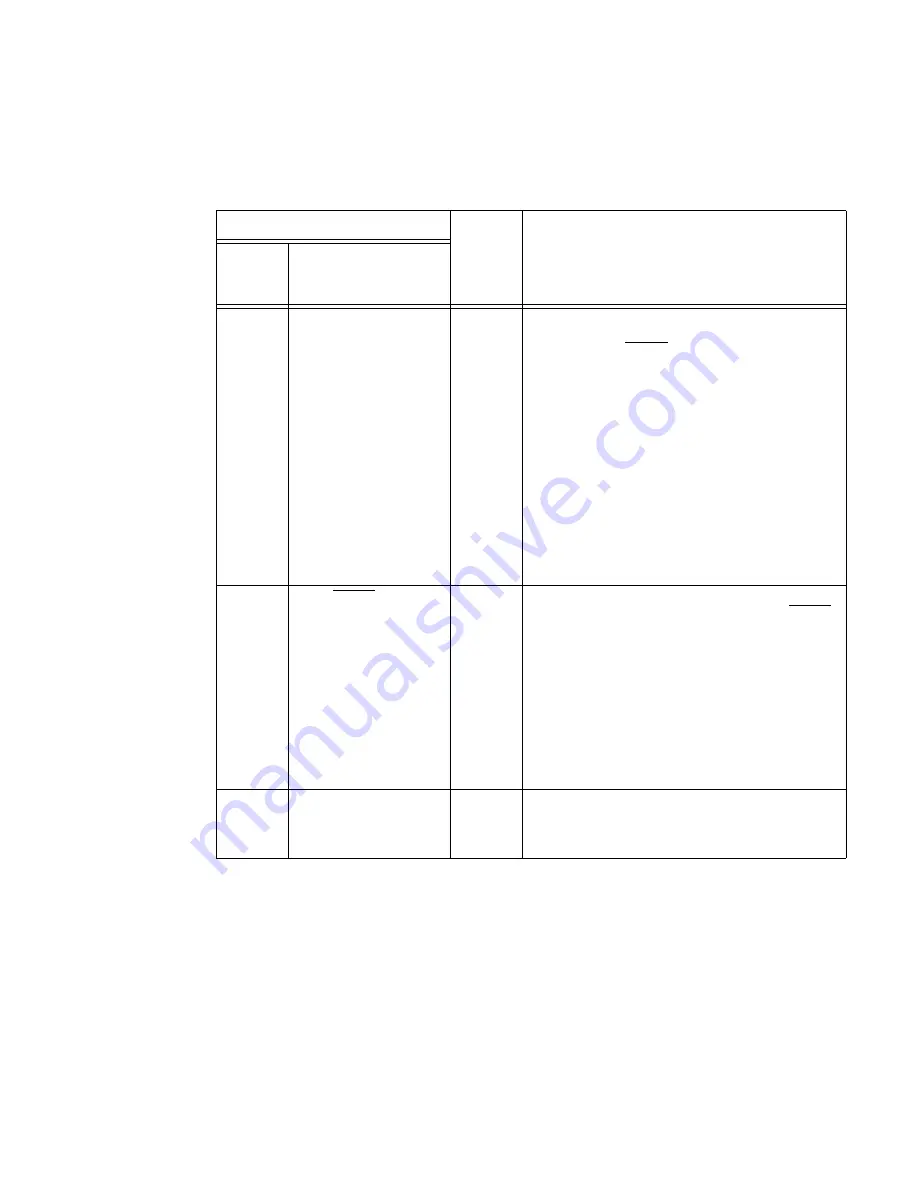

Communications Processor Module (CPM) Ports

PA8

SMC2: SMRXD

SI1 TDMA1: L1RXD0

TDM nibble

SI1 TDMA1: L1RXD

TDM serial

Input

Input

Input

SMC2: Serial Management Receive Data

Supported by SMC2. The SMC interface consists of

SMTXD, SMRXD, SMSYN, and a clock. Not all signals are

used for all applications. SMCs are full-duplex ports that

supports three protocols or modes: UART, transparent, or

general-circuit interface (GCI).

Time-Division Multiplexing A1: Layer 1 Nibble Receive

Data Bit 0

In the TDMA1 interface supported by SI1. L1RXD3 is the

most significant bit. L1RXD0 is the least significant bit in

nibble mode. TDMA1 receives nibble data from

L1RXD[0–3].

Time-Division Multiplexing A1: Layer 1 Serial Receive

Data

In the TDMA1 interface supported by SI1. TDMA1 receives

serial data from L1RXD.

PA7

SMC2: SMSYN

SI1 TDMA1: L1TSYNC

TDM nibble

and

TDM serial

Input

Input

SMC2: Serial Management Synchronization

The SMC interface consists of SMTXD, SMRXD, SMSYN,

and a clock. Not all signals are used for all applications.

SMCs are full-duplex ports that supports three protocols or

modes: UART, transparent, or general-circuit interface

(GCI).

Time-Division Multiplexing A1: Layer 1 Transmit

Synchronization

In the TDMA1 interface supported by SI1, this is the

synchronizing signal for the transmit channel. See the

Serial

Interface with Time-Slot Assigner

chapter in the

MSC8101

Technical Reference

manual.

PA6

SI1 TDMA1: L1RSYNC

TDM nibble

and

TDM serial

Input

Time-Division Multiplexing A1: Layer 1 Receive

Synchronization.

In the TDMA1 interface supported by SI1, this is the

synchronizing signal for the receive channel.

Table 1-3. Port A Signals (Continued)

Name

Dedicated

I/O Data

Direction

Description

General-

Purpose

I/O

Peripheral Controller:

Dedicated Signal

Protocol