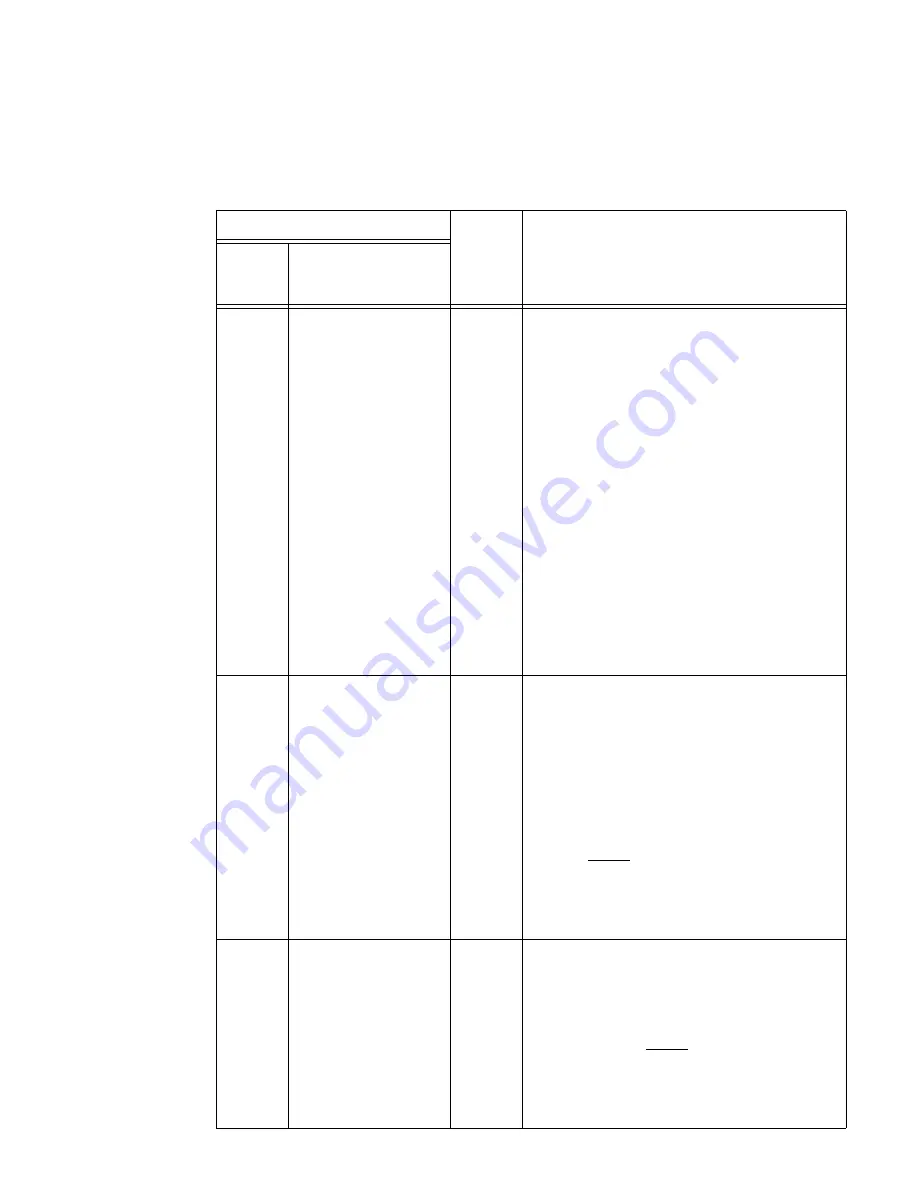

1-44

Communications Processor Module (CPM) Ports

PD18

FCC1: RXADDR4

UTOPIA master

FCC1: RXADDR4

UTOPIA slave

FCC1: RXCLAV3

UTOPIA multi-PHY master,

direct polling

SPI: SPICLK

Output

Input

Input

Input/

Output

FCC1: UTOPIA Master Receive Address Bit 4

In the ATM UTOPIA master interface supported by FCC1

using multiplexed polling, this is receive address bit 4.

FCC1: UTOPIA Slave Receive Address Bit 4

In the ATM UTOPIA slave interface supported by FCC1,

this is the receive address bit 4.

FCC1: UTOPIA Multi-PHY Master Receive Cell Available

3 Direct Polling

In the ATM UTOPIA master interface supported by FCC1

using direct polling, RXCLAV3 is asserted by an external

PHY when one complete ATM cell is available for transfer.

SPI: Clock

The SPI interface comprises four signals: master out slave

in (SPIMOSI), master in slave out (SPIMISO), clock

(SPICLK) and select (SPISEL). The SPI can be configured

as a slave or master in single- or multiple-master

environments. SPICLK is a gated clock, active only during

data transfers. Four combinations of SPICLK phase and

polarity can be configured. When the SPI is a master,

SPICLK is the clock output signal that shifts received data in

from SPIMISO and transmitted data out to SPIMOSI.

PD17

BRG2O

FCC1: RXPRTY

UTOPIA

SPI: SPIMOSI

Output

Input

Input/

Output

Baud Rate Generator 2 Output

The CPM supports up to 8 BRGs. The BRGs can be used

internally to the MSC8101 and/or provide an output to one

of the 8 BRG pins.

FCC1: UTOPIA Receive Parity

In the ATM UTOPIA interface supported by FCC1, this is

the odd parity bit for RXD[0–7].

SPI: Master Output Slave Input

The SPI interface comprises our signals: master out slave in

(SPIMOSI), master in slave out (SPIMISO), clock (SPICLK)

and select (SPISEL). The SPI can be configured as a slave

or master in single- or multiple-master environments. When

the SPI is a slave, SPICLK is the clock input that shifts

received data in from SPIMOSI and transmitted data out

through SPIMISO.

PD16

FCC1: TXPRTY

UTOPIA

SPI: SPIMISO

Output

Input/

Output

FCC1: UTOPIA Transmit Parity

In the ATM UTOPIA interface supported by FCC1, this is

the odd parity bit for TXD[0–7].

SPI: Master Input Slave Output

The SPI interface comprises four signals: master out slave

in (SPIMOSI), master in slave out (SPIMISO), clock

(SPICLK), and select (SPISEL). The SPI can be configured

as a slave or master in single- or multiple-master

environments. When the SPI is a slave, SPICLK is the clock

input that shifts received data in from SPIMOSI and

transmitted data out through SPIMISO.

Table 1-6. Port D Signals (Continued)

Name

Dedicated

I/O Data

Direction

Description

General-

Purpose

I/O

Peripheral Controller:

Dedicated I/O

Protocol