2-7

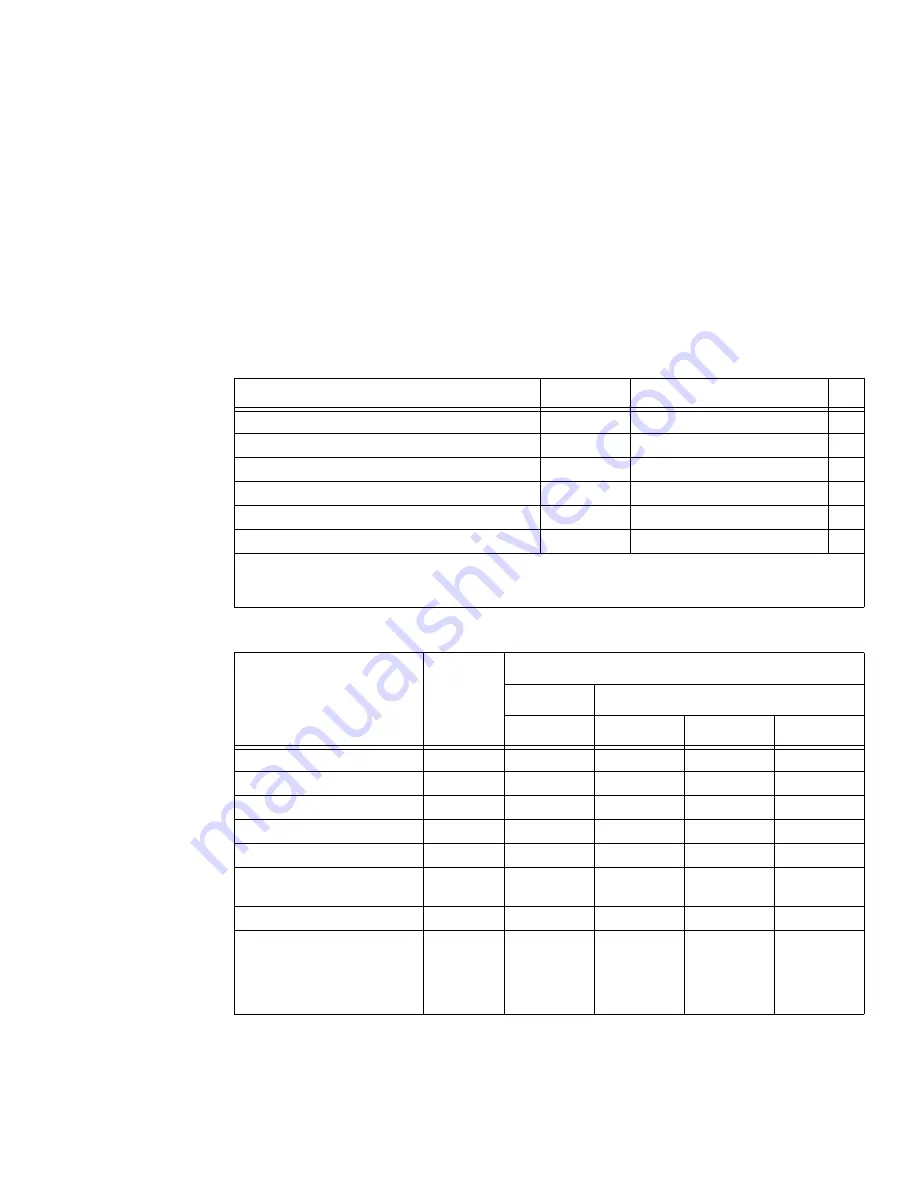

AC Timings

2.7 AC Timings

The following sections include illustrations and tables of clock diagrams, signals, and parallel I/O outputs

and inputs. AC timings are based on a 50 pF load, except where noted otherwise, and 50

Ω

transmission

line.

2.7.1 Clocking and Timing Characteristics

Table 2-9. System Clock Parameters

Characteristic Minimum

Maximum

Unit

Phase Jitter between BCLK and DLLIN

—

0.5

ns

CLKIN frequency

1,2

18

75

MHz

CLKIN slope

—

5

ns

DLLIN slope

—

2

ns

CLKOUT frequency jitter

—

(0.01

×

CLKOUT) + CLKIN jitter

ns

Delay between CLKOUT and DLLIN

—

5

ns

Notes:

1.

Low CLKIN frequency causes poor PLL performance. Choose a CLKIN frequency high enough to keep

the frequency after the predivider (SPLLMFCLK) higher than 18 MHz.

2.

CLKIN should have a 50%

±

5% duty cycle.

Table 2-10. Clock Ranges

Clock

Symbol

Maximum Rated Core Frequency

All

Max. Values for SC140 Clock Rating of:

Min

250 MHz

275 MHz

300 MHz

Input Clock

CLKIN

18 MHz

62.5

68.75 MHz

75 MHz

SPLL MF Clock

SPLLMFCLK

18 MHz

20.83

22.9 MHz

25 MHz

Bus

BCLK

18 MHz

62.5 MHz

68.75 MHz

75 MHz

Output

CLKOUT

43.2 MHz

62.5 MHz

68.75 MHz

75 MHz

Serial Communications Controller

SCLK

18 MHz

62.5 MHz

68.75 MHz

75 MHz

Communications Processor

Module

CPMCLK

36 MHz

125 MHz

137.5 MHz

150 MHz

SC140 Core

DSPCLK

72 MHz

250 MHz

275 MHz

300 MHz

Baud Rate Generator

•

For BRG DF = 4

•

For BRG DF = 16 (default)

•

For BRG DF = 64

•

For BRG DF = 256

BRGCLK

36 MHz

9 MHz

2.25 MHz

562.5 KHz

62.5 MHz

15.63 MHz

3.91 MHz

976.6 KHz

68.75 MHz

17.19 MHz

4.30 MHz

1.07 MHz

75 MHz

18.75 MHz

4.69 MHz

1.17 MHz