2-12

AC Timings

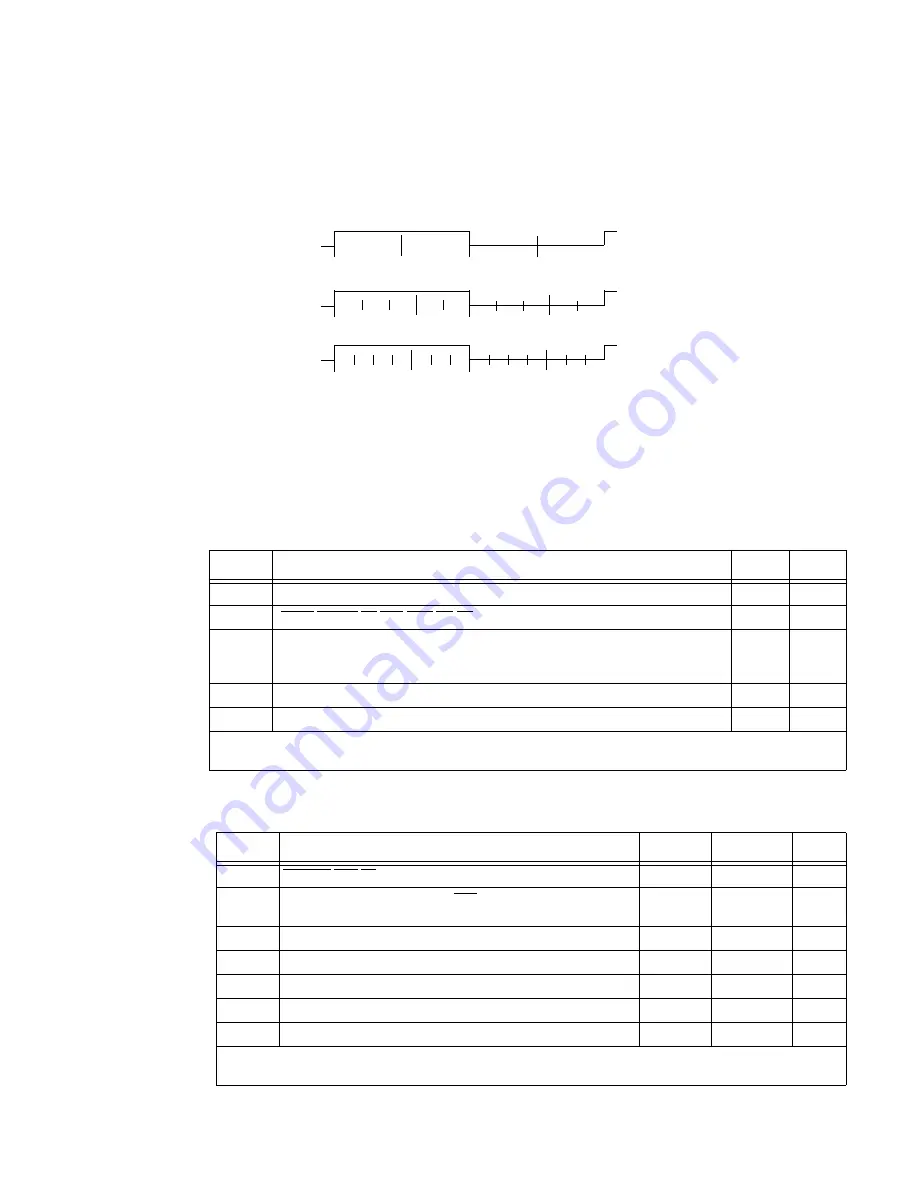

Figure 2-5 is a graphical representation of Table 2-14.

Note:

The UPM machine and GPCM machine outputs change on the internal tick determined by the

memory controller programming; the AC specifications are relative to the internal tick. SDRAM

machine outputs change only on the

REFCLK

rising edge.

Figure 2-5. Internal Tick Spacing for Memory Controller Signals

Table 2-15. AC Characteristics for SIU Inputs

Number

Characteristic Value

Units

10

Hold time for all signals after REFCLK rising edge

0.5

ns

11

AACK/ARTRY/TA/TEA/DBG/BG/BR setup time before REFCLK rising edge

5

ns

12

Data bus setup time before REFCLK rising edge

a. Normal mode

b. ECC and parity mode

4.55

6

ns

ns

14

DP setup time before REFCLK rising edge

6

ns

15

Setup time before REFCLK rising edge for all other signals

4

ns

Note:

Input specifications are measured from the TTL signal level (0.8 or 2.0 V) relative to the REFCLK rising

edge.

Table 2-16. AC Characteristics for SIU Outputs

Number

Characteristic Maximum

Minimum

Units

31 PSDVAL/TEA/TA delay from REFCLK rising edge

9

1.0

ns

32a

Address bus/Address attributes/GBL delay from REFCLK rising

edge

8.5

1.0

ns

32b

BADDR delay from REFCLK rising edge

10

1.0

ns

33a

Data bus delay from REFCLK rising edge

8.5

1.0

ns

33b

DP delay from REFCLK rising edge

10

1.0

ns

34

Memory controller signals/ALE delay from REFCLK rising edge

5.5

1.0

ns

35

All other signals delay from REFCLK rising edge

6

1.0

ns

Note:

Output specifications are measured from the 1.4 V level of the REFCLK rising edge to the TTL signal level

(0.8 or 2.0 V).

REFCLK

T1

T2

T3

T4

REFCLK

T1

T2

T3

T4

for 1:2.5

for 1:3.5

REFCLK

T1

T2

T3

T4

for 1:2, 1:3, 1:4, 1:5, 1:6