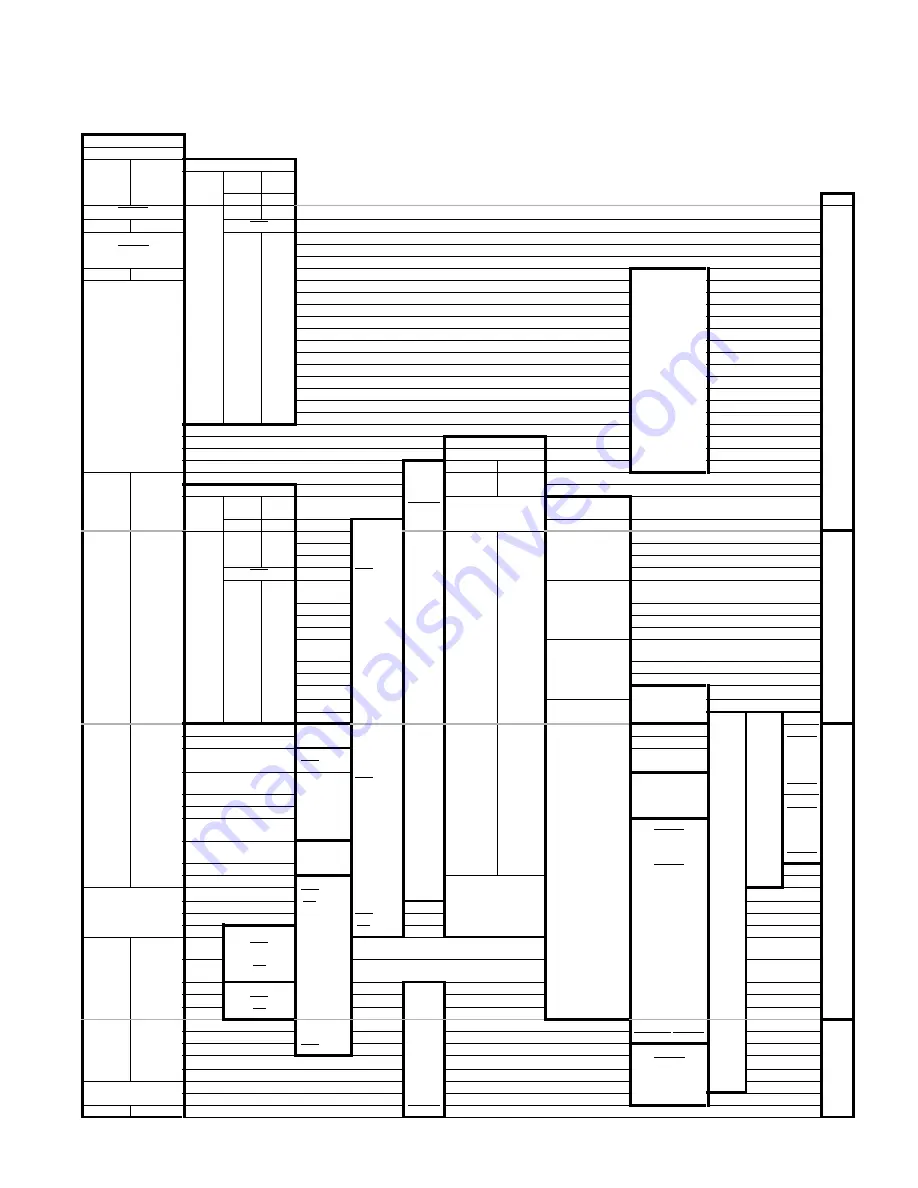

1-3

Signal Groupings

FCC1

ATM/UTOPIA

MPHY

Master

mux poll

or Slave

MPHY

Master

dir. poll

FCC1

Ethernet

MII

HDLC/

transp.

HDLC

Serial

Nibble

GPIO

TXENB

COL

PA31

TXCLAV

TXCLAV0

CRS

RTS

PA30

TXSOC

TX_ER

PA29

RXENB

TX_EN

PA28

RXSOC

RX_DV

PA27

RXCLAV

RXCLAV0

RX_ER

SDMA

PA26

TXD0

MSNUM0

PA25

TXD1

MSNUM1

PA24

TXD2

PA23

TXD3

PA22

TXD4

TXD3

TXD3

PA21

TXD5

TXD2

TXD2

PA20

TXD6

TXD1

TXD1

PA19

TXD7

TXD0

TXD

TXD0

PA18

RXD7

RXD0

RXD

RXD0

PA17

RXD6

RXD1

RXD1

PA16

RXD5

RXD2

RXD2

PA15

RXD4

RXD3

RXD3

PA14

RXD3

MSNUM2

PA13

RXD2

SI1

MSNUM3

PA12

RXD1

TDMA1

MSNUM4

PA11

RXD0

SMC2

Serial

Nibble

MSNUM5

PA10

SMTXD

L1TXD

L1TXD0

PA9

FCC2

SMRXD

L1RXD

L1RXD0

PA8

Ethernet

MII

HDLC/

transp.

HDLC

SMSYN

L1TSYNC

SI2

PA7

Serial

Nibble

SCC2

L1RSYNC

TDMB2

PA6

TX_ER

RXD

L1TXD

PB31

RX_DV

TXD

L1RXD

PB30

TX_EN

L1RSYNC

PB29

RX_ER

RTS

RTS/TENA

L1TSYNC

PB28

COL

TDMC2

L1TXD

PB27

CRS

L1RXD

PB26

TXD3

TXD3

L1TXD3

L1TSYNC

PB25

TXD2

TXD2

L1RXD3

L1RSYNC

PB24

TXD1

TXD1

L1RXD2

TDMD2

L1TXD

PB23

TXD0

TXD

TXD0

L1RXD1

L1RXD

PB22

RXD0

RXD

RXD0

L1TXD2

L1TSYNC

PB21

RXD1

RXD1

L1TXD1

L1RSYNC

I

2

C

PB20

RXD2

RXD2

SDA

PB19

RXD3

RXD3

SCL

BRGs

Clocks Timers

PB18

Ext. Req.

BRG1O

CLK1

TGATE1 PC31

EXT1

BRG2O

CLK2

TOUT1

PC30

SCC1

CTS/CLSN

BRG3O

CLK3

TIN2

PC29

CTS/CLSN

SIU Timer Input

BRG4O

CLK4

TIN1/

TOUT2

PC28

CLK5

BRG5O

CLK5

TGATE2 PC27

TMCLK

BRG6O

CLK6

TOUT3

PC26

DMA

DACK2

BRG7O

CLK7

TIN4

PC25

Ext. Req.

DREQ2

BRG8O

CLK8

TIN3/

TOUT4

PC24

EXT2

DACK1

CLK9

PC23

SCC1

LIST1

DREQ1

CLK10

PC22

TXADDR0

CTS/CLSN

SMTXD

PC15

RXADDR0

CD/RENA

LIST2

PC14

TXADDR1

CTS/CLSN

LIST4

PC13

RXADDR1

FCC1

CD/RENA

LIST3

PC12

TXADDR2

TXADDR2/

TXCLAV1

CTS

LIST1

PC7

RXADDR2

RXADDR2/

RXCLAV1

CD

LIST2

PC6

FCC2

SMC1

CTS

SMTXD

LIST3

PC5

CD

SMRXD

LIST4

PC4

RXD

DRACK1/DONE1

PD31

TXD

DRACK2/DONE2

PD30

RXADDR3

RXCLAV2

RTS/TENA

SPI

PD29

TXADDR4

TXCLAV3

SPISEL

BRG1O

PD19

RXADDR4

RXCLAV3

SPICLK

PD18

RXPRTY

SPIMOSI

BRG2O

PD17

TXPRTY

SPIMISO

PD16

TXADDR3

TXCLAV2

SMSYN

PD7

Figure 1-2. CPM Port A–D Pin Multiplexed Functionality