Programming Model

MOTOROLA

Bluetooth Accelerator (BTA)

16-27

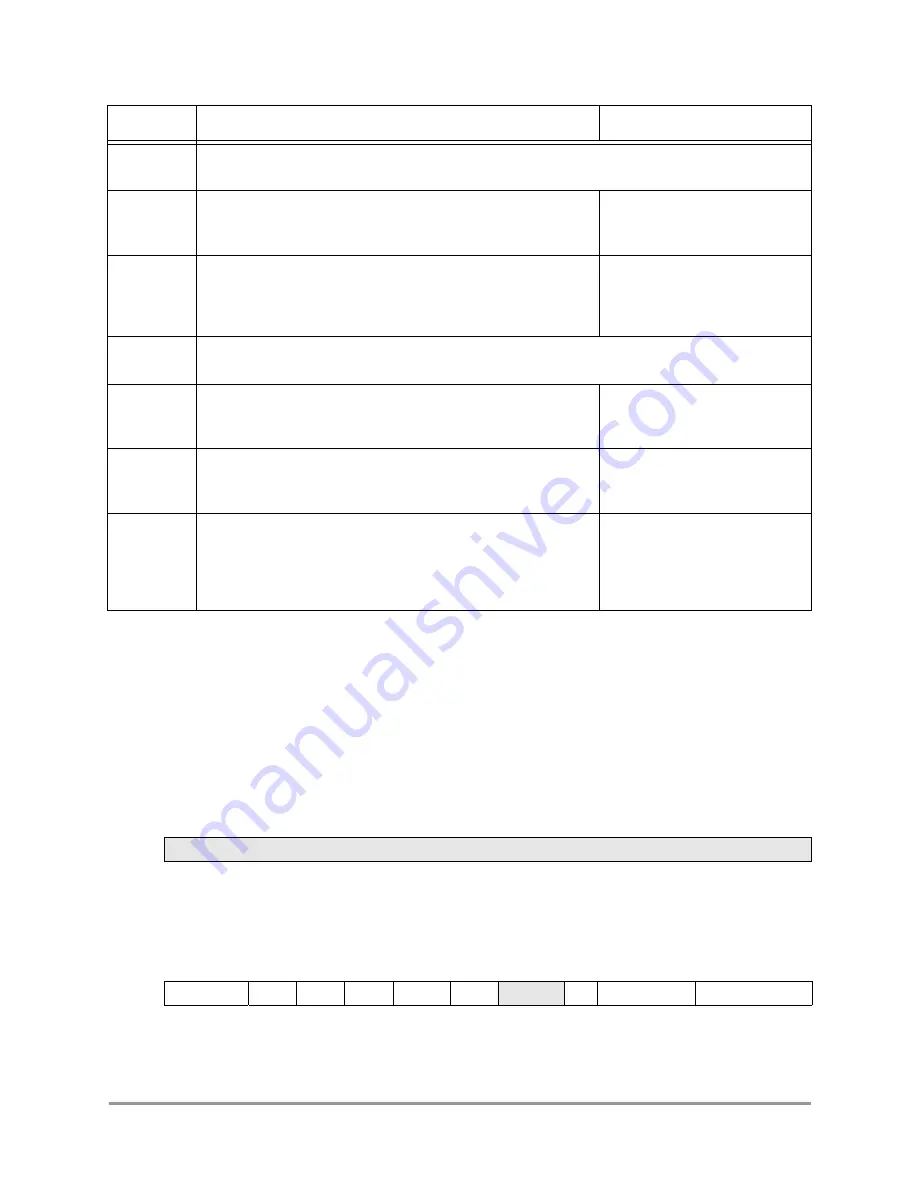

16.5.1.2 Status Register

The read-only Status Register returns status information about the BTA, including the lower two bits of the

Bluetooth clock, information about FEC and CRC errors, the current operating state of the BTA and the

long word bit buffer currently used by the BTA. The Status Register bits and their settings are described in

Table 16-13 on page 16-28.

Reserved

Bits 11–7

Reserved—These bits are reserved and should read 0.

OS

Bit 6

Override ESTIMATEDCLK 2 LSBs

—Overrides the two least

significant bits of the ESTIMATEDCLK when a trigger is received

by the unit operating as a slave during synchronization.

0 = Preset the two LSBs to 00

1 = Do not preset the two LSBs

CWS

Bit 5

Correlation Window Size

—Selects the correlation window size.

When window search is selected (CWS is cleared), the window

size is controlled by the TX_TIME and RX_TIME Registers. (see

section 16.5.4.10 and 16.5.4.11 respectively for details).

0 = Window search

1 = Continuous search

Reserved

Bit 4

Reserved—This bit is reserved and should read 0.

IDP

Bit 3

ID Packet

—Indicates that the packet to transmit is an ID packet

(as specified in the Bluetooth specification) that contains only the

access code.

0 = Non ID packet type

1 = ID packet type

MS

Bit 2

NATIVECLK/ESTIMATEDCLK Selection

—Determines which of

the two clocks maintained by the Bluetooth core is used as

SYSTICK.

0 = ESTIMATEDCLK

1 = NATIVECLK

CMD

Bits 1–0

Command

—Determines the BTA’s mode of operation.

00 = Idle

01 = Receive

10 = Transmit

11 = Continuous Rx/Tx test

mode

STATUS

Status Register

Addr

0x00216000

BIT

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

TYPE

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0x0000

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

MS2LSB

REC1

REC2

NREC

CRC16

HEC8

MS

STATE

BUF_ADDR

TYPE

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

RESET

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0x0040

Table 16-12. Command Register Description (Continued)

Name

Description

Settings

Summary of Contents for DragonBall MC9328MX1

Page 68: ...1 12 MC9328MX1 Reference Manual MOTOROLA Introduction ...

Page 86: ...2 18 MC9328MX1 Reference Manual MOTOROLA Signal Descriptions and Pin Assignments ...

Page 116: ...3 30 MC9328MX1 Reference Manual MOTOROLA Memory Map ...

Page 126: ...4 10 MC9328MX1 Reference Manual MOTOROLA ARM920T Processor ...

Page 160: ...8 8 MC9328MX1 Reference Manual MOTOROLA System Control ...

Page 272: ...13 32 MC9328MX1 Reference Manual MOTOROLA DMA Controller ...

Page 281: ...Programming Model MOTOROLA Watchdog Timer Module 14 9 ...

Page 282: ...14 10 MC9328MX1 Reference Manual MOTOROLA Watchdog Timer Module ...

Page 300: ...15 18 MC9328MX1 Reference Manual MOTOROLA Analog Signal Processor ASP ...

Page 438: ...18 16 MC9328MX1 Reference Manual MOTOROLA Serial Peripheral Interface Modules SPI 1 and SPI 2 ...

Page 478: ...19 40 MC9328MX1 Reference Manual MOTOROLA LCD Controller ...

Page 574: ...21 32 MC9328MX1 Reference Manual MOTOROLA Memory Stick Host Controller MSHC Module ...

Page 598: ...23 16 MC9328MX1 Reference Manual MOTOROLA Real Time Clock RTC ...

Page 670: ...24 72 MC9328MX1 Reference Manual MOTOROLA SDRAM Memory Controller ...

Page 726: ...25 56 MC9328MX1 Reference Manual MOTOROLA SmartCard Interface Module SIM ...

Page 736: ...26 10 MC9328MX1 Reference Manual MOTOROLA General Purpose Timers ...

Page 854: ...29 18 MC9328MX1 Reference Manual MOTOROLA I2C Module ...

Page 900: ...30 46 MC9328MX1 Reference Manual MOTOROLA Synchronous Serial Interface SSI ...

Page 942: ...32 26 MC9328MX1 Reference Manual MOTOROLA GPIO Module and I O Multiplexer IOMUX ...