Programming Model

MOTOROLA

SmartCard Interface Module (SIM)

25-29

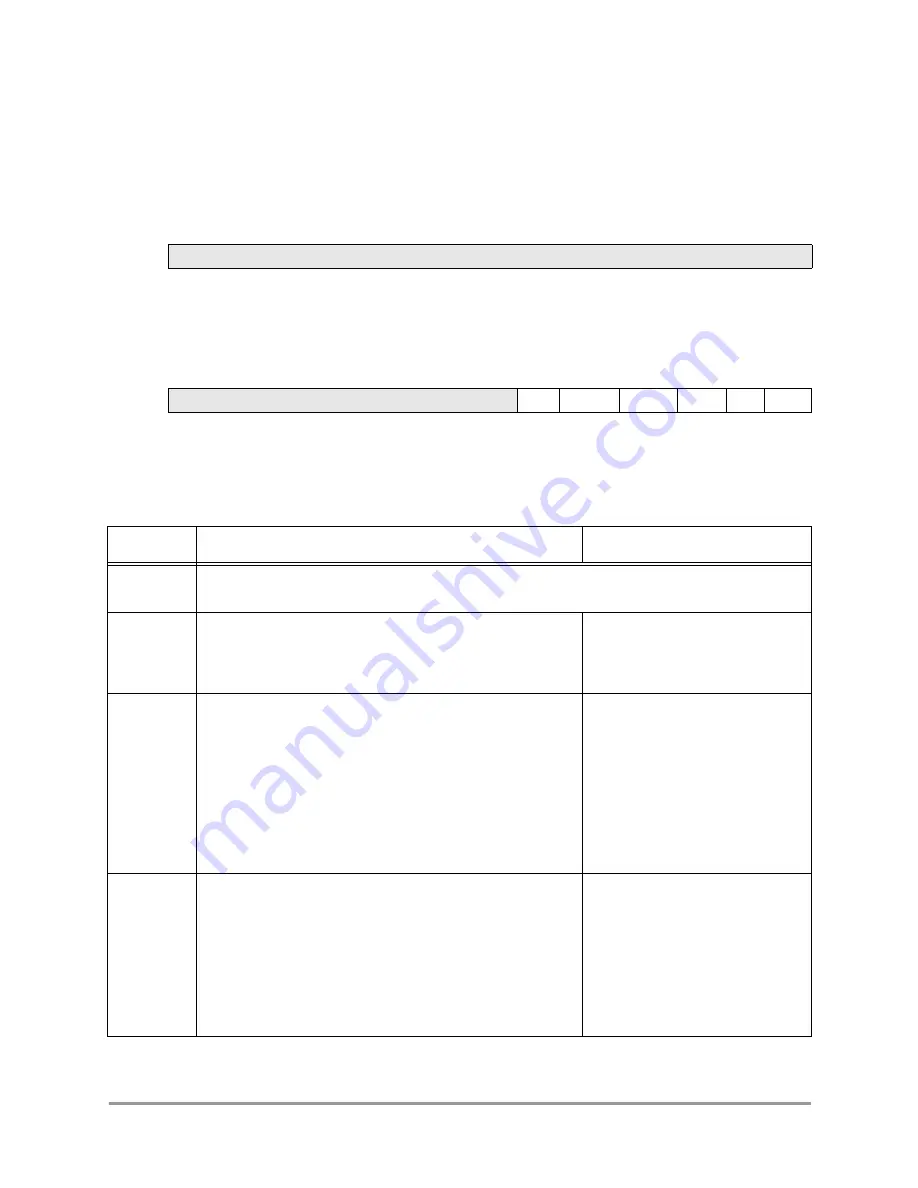

25.6.6 Receive Status Register

The Receive Status Register (RCV_STATUS) provides the status of the SIM receiver and its FIFO. The bit

descriptions and settings for the Receive Status Register are provided in Table 25-14.

RCV_STATUS

Receive Status Register

Addr

0x00211014

BIT

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

TYPE

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

RESET

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0x0000

BIT

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

CWT

CRCOK

LRCOK

RDRF

RFD

OEF

TYPE

r

r

r

r

r

r

r

r

r

r

rw

r

r

r

r

rw

RESET

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0x0008

Table 25-14. Receive Status Register Description

Name

Description

Settings

Reserved

Bits 31–6

Reserved—These bits are reserved and should read 0.

CWT

Bit 5

Character Wait Time Counter Flag

—Indicates when the

time between received characters is equal to or greater than

the value programmed in the CHAR_WAIT register.

0

=

No CWT violation has occurred

1

=

Time between two consecutive

characters exceeded the value

in CHAR_WAIT

CRCOK

Bit 4

Cyclic Redundancy Check Okay Flag

—Indicates when the

calculated 16-bit CRC value matches the expected value for

the current input data stream. The value is calculated across

all received characters from the point the CRCEN bit is set in

the CNTL register. The current CRC residual is reset by three

actions:

•

Clear the CRCEN bit in the CNTL register

•

Set the XMT_EN bit in the ENABLE register

•

Automatically reset by hardware when the ETC flag is

set at the end of a transmission.

0

=

Current CRC value does not

match remainder

1

=

Current calculated CRC value

matches the expected result

LRCOK

Bit 3

Linear Redundancy Check Okay Flag

—Indicates when the

calculated 8-bit LRC value is zero value for the current input

data stream. The value is calculated across all received

characters from the point the LRCEN bit is set in the CNTL

register. The current LRC residual is reset by three actions:

•

Clear the LRCEN bit in CNTL register

•

Set the XMT_EN bit in the ENABLE register

•

Automatically reset by hardware when ETC flag is set

at the end of a transmission.

0

=

Current LRC value does not

match remainder

1

=

Current calculated LRC value

matches the expected result

(zero)

Summary of Contents for DragonBall MC9328MX1

Page 68: ...1 12 MC9328MX1 Reference Manual MOTOROLA Introduction ...

Page 86: ...2 18 MC9328MX1 Reference Manual MOTOROLA Signal Descriptions and Pin Assignments ...

Page 116: ...3 30 MC9328MX1 Reference Manual MOTOROLA Memory Map ...

Page 126: ...4 10 MC9328MX1 Reference Manual MOTOROLA ARM920T Processor ...

Page 160: ...8 8 MC9328MX1 Reference Manual MOTOROLA System Control ...

Page 272: ...13 32 MC9328MX1 Reference Manual MOTOROLA DMA Controller ...

Page 281: ...Programming Model MOTOROLA Watchdog Timer Module 14 9 ...

Page 282: ...14 10 MC9328MX1 Reference Manual MOTOROLA Watchdog Timer Module ...

Page 300: ...15 18 MC9328MX1 Reference Manual MOTOROLA Analog Signal Processor ASP ...

Page 438: ...18 16 MC9328MX1 Reference Manual MOTOROLA Serial Peripheral Interface Modules SPI 1 and SPI 2 ...

Page 478: ...19 40 MC9328MX1 Reference Manual MOTOROLA LCD Controller ...

Page 574: ...21 32 MC9328MX1 Reference Manual MOTOROLA Memory Stick Host Controller MSHC Module ...

Page 598: ...23 16 MC9328MX1 Reference Manual MOTOROLA Real Time Clock RTC ...

Page 670: ...24 72 MC9328MX1 Reference Manual MOTOROLA SDRAM Memory Controller ...

Page 726: ...25 56 MC9328MX1 Reference Manual MOTOROLA SmartCard Interface Module SIM ...

Page 736: ...26 10 MC9328MX1 Reference Manual MOTOROLA General Purpose Timers ...

Page 854: ...29 18 MC9328MX1 Reference Manual MOTOROLA I2C Module ...

Page 900: ...30 46 MC9328MX1 Reference Manual MOTOROLA Synchronous Serial Interface SSI ...

Page 942: ...32 26 MC9328MX1 Reference Manual MOTOROLA GPIO Module and I O Multiplexer IOMUX ...