Device Identification Register (IDR)

Core Configuration

4

-37

4.8

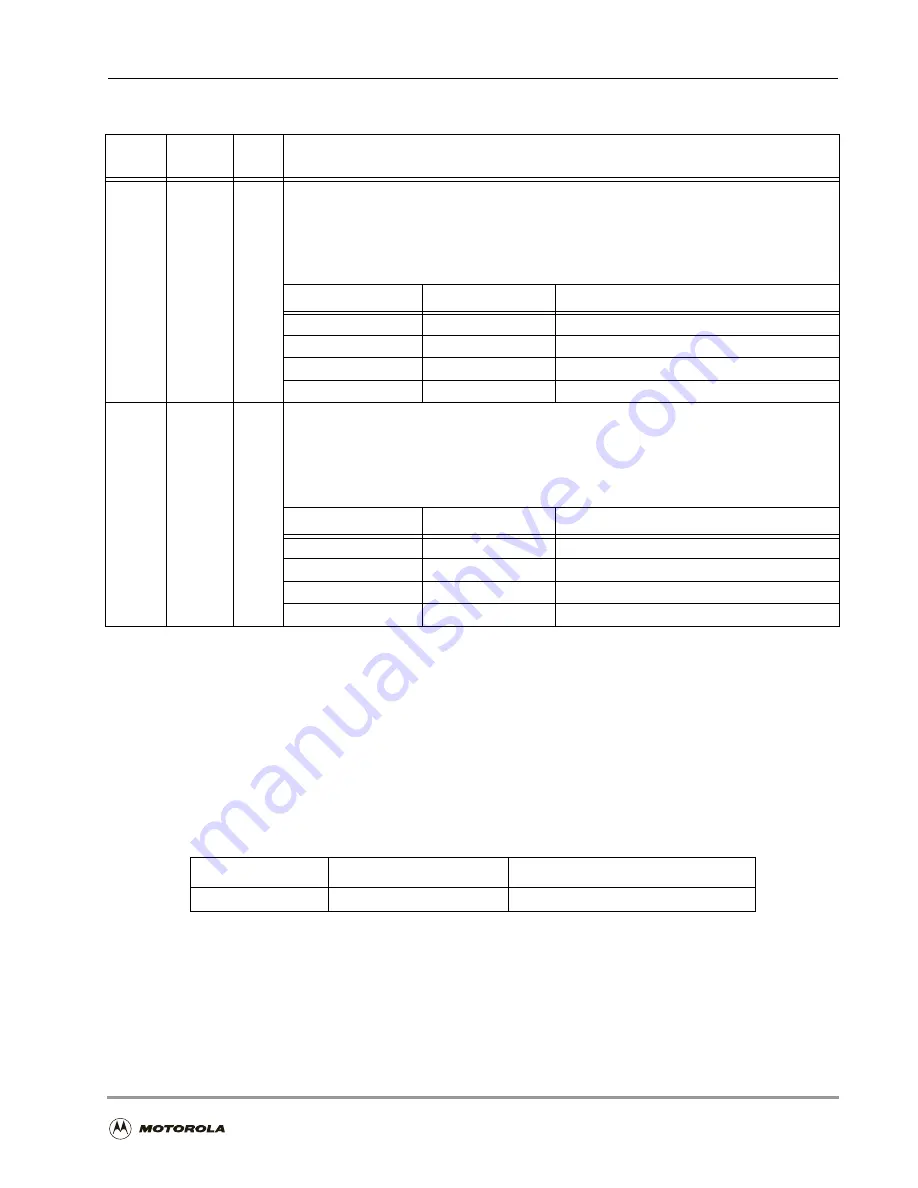

Device Identification Register (IDR)

The IDR is a read-only factory-programmed register that identifies DSP56300 family

members. It specifies the derivative number and revision number of the device. This

information is used in testing or by software. Figure 4-10 shows the contents of the IDR.

Revision numbers are assigned as follows: $0 is revision 0, $1 is revision A, and so on.

.

Figure 4-10. Identification Register Configuration (Revision E)

3–2

DDS[1–0]

0

DMA Destination Space

Specify the memory space referenced as a destination by the DMA.

NOTE: In Cache mode, a DMA to Program memory space has some limitations (as

described in Chapter 8,

Instruction Cache, and Chapter 11, Operating Modes and Memory

Spaces).

DDS1

DDS0

DMA Destination Memory Space

0

0

X Memory Space

0

1

Y Memory Space

1

0

P Memory Space

1

1

Reserved

1–0

DSS[1–0]

0

DMA Source Space

Specify the memory space referenced as a source by the DMA.

NOTE: In Cache mode, a DMA to Program memory space has some limitations (as

described in Chapter 8,

Instruction Cache, and Chapter 11, Operating Modes and Memory

Spaces).

DSS1

DSS0

DMA Source Memory Space

0

0

X Memory Space

0

1

Y Memory Space

1

0

P Memory Space

1

1

Reserved

23

16

15

12

11

0

Reserved

Revision Number

Derivative Number

$00

$5

$303

Table 4-11. DMA Control Register (DCR) Bit Definitions (Continued)

Bit

Number

Bit Name

Reset

Value

Description

Summary of Contents for DSP56303

Page 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Page 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Page 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Page 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Page 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Page 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Page 320: ...Index 14 DSP56303 User s Manual ...