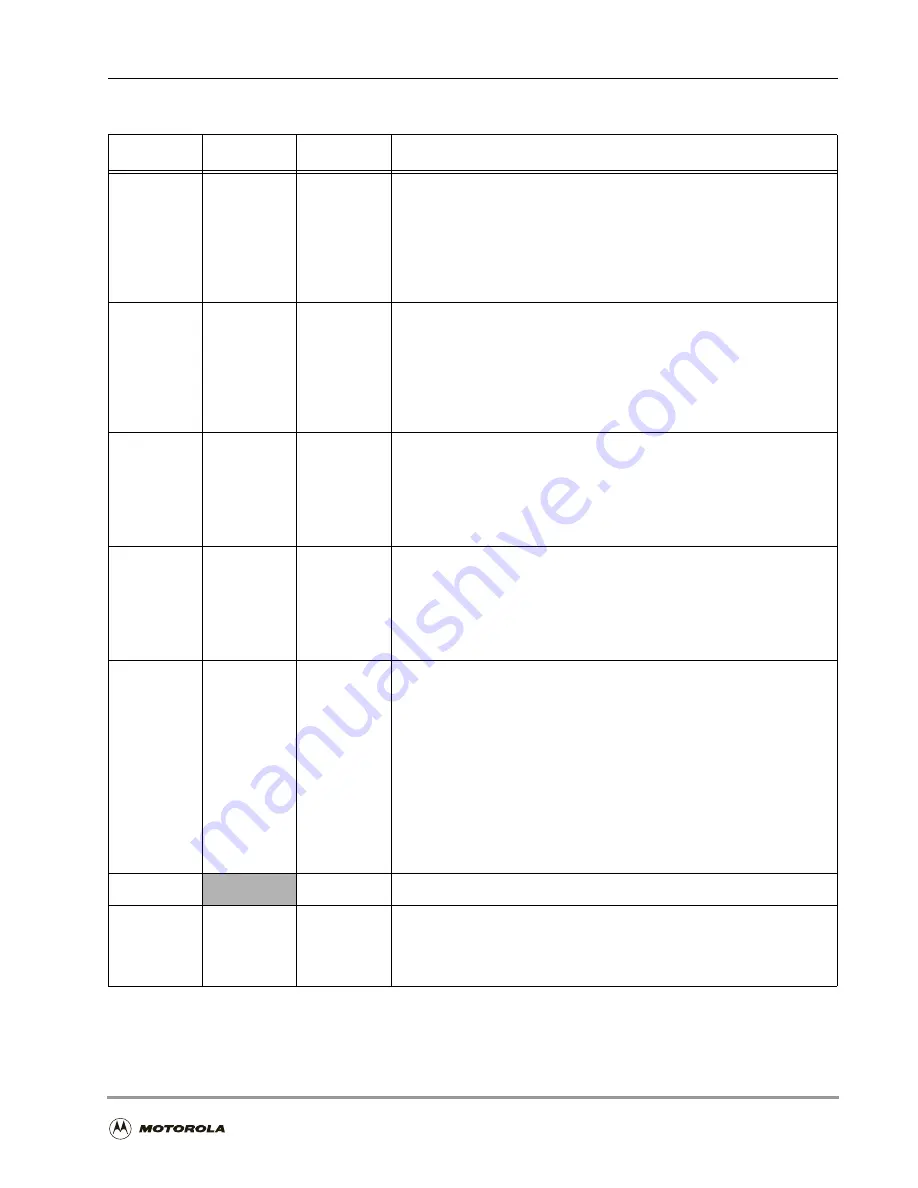

DSP Core Programming Model

Host Interface (HI08)

6

-19

12

HDDS

0

Host Dual Data Strobe

If the HDDS bit is cleared, the HI08 operates in single-strobe bus mode. In

this mode, the bus has a single data strobe signal for both reads and

writes. If the HDDS bit is set, the HI08 operates in dual strobe bus mode.

In this mode, the bus has two separate data strobes: one for data reads,

the other for data writes. See Figure 6-13 on page 6-21 and Figure 6-14

on page 6-21 for details on dual and single strobe modes.

11

HMUX

0

Host Multiplexed Bus

If HMUX is set, the HI08 operates in multiplex mode, latching the lower

portion of a multiplexed address/data bus. In this mode the internal

address line values of the host registers are taken from the internal latch.

If HMUX is cleared, it indicates that the HI08 is connected to a

non-multiplexed type of bus. The values of the address lines are then

taken from the HI08-dedicated address signals.

10

HASP

0

Host Address Strobe Polarity

If HASP is cleared, the host address strobe (HAS) signal is an active low

input, and the address on the host address/data bus is sampled when the

HAS signal is low. If HASP is set, HAS is an active-high address strobe

input, and the address on the host address or data bus is sampled when

the HAS signal is high.

9

HDSP

0

Host Data Strobe Polarity

If HDSP is cleared, the data strobe signals are configured as active low

inputs, and data is transferred when the data strobe is low. If HDSP is set,

the data strobe signals are configured as active high inputs, and data is

transferred when the data strobe is high. The data strobe signals are

either HDS by itself or both HRD and HWR together.

8

HROD

0

Host Request Open Drain

Controls the output drive of the host request signals. In the single host

request mode (that is, when HDRQ is cleared in ICR), if HROD is cleared

and host requests are enabled (that is, if HREN is set and HEN is set in

the host port control register (HPCR)), then the HREQ signal is always

driven by the HI08. If HROD is set and host requests are enabled, the

HREQ signal is an open drain output. In the double host request mode

(that is, when HDRQ is set in the ICR), if HROD is cleared and host

requests are enabled (that is, if HREN is set and HEN is set in the HPCR),

then the HTRQ and HRRQ signals are always driven. If HROD is set and

host requests are enabled, the HTRQ and HRRQ signals are open drain

outputs.

7

0

Reserved. Write to 0 for future compatibility.

6

HEN

0

Host Enable

If HEN is set, the HI08 operates as the host interface. If HEN is cleared,

the HI08 is not active, and all the HI08 signals are configured as GPIO

signals according to the value of the HDDR and HDR.

Table 6-12. Host Port Control Register (HPCR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description

Summary of Contents for DSP56303

Page 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Page 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Page 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Page 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Page 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Page 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Page 320: ...Index 14 DSP56303 User s Manual ...