Host Programmer Model

Host Interface (HI08)

6

-29

6.7.4

Interrupt Vector Register (IVR)

The IVR is an 8-bit read/write register that typically contains the interrupt vector number used

with MC68000 family processor vectored interrupts. Only the host processor can read and

write this register. The contents of the IVR are placed on the host data bus, H[7–0], when both

the

HREQ

and

HACK

signals are asserted. The contents of this register are initialized to $0F by

a hardware or software reset. This value corresponds to the uninitialized interrupt vector in

the MC68000 family.

1

TXDE

1

Transmit Data Register Empty

Indicates that the transmit byte registers (TXH:TXM:TXL) are empty and

can be written by the host processor. TXDE is set when the contents of

the transmit byte registers are transferred to the HRX register. TXDE is

cleared when the transmit register (TXL or TXH according to HLEND bit)

is written by the host processor. The host processor can set TXDE using

the initialize function. TXDE can assert the external HTRQ signal if the

TREQ bit is set. Regardless of whether the TXDE interrupt is enabled,

TXDE indicates whether the TX registers are full and data can be latched

in (so that polling techniques may be used by the host processor).

Hardware, software, individual, and stop resets all set TXDE.

0

RXDF

0

Receive Data Register Full

Indicates that the receive byte registers (RXH:RXM:RXL) contain data

from the DSP56303 to be read by the host processor. RXDF is set when

the HTX is transferred to the receive byte registers. RXDF is cleared when

the host processor reads the receive data register (RXL or RXH according

to HLEND bit). The host processor can clear RXDF using the initialize

function. RXDF can assert the external HREQ signal if the RREQ bit is

set. Regardless of whether the RXDF interrupt is enabled, RXDF indicates

whether the RX registers are full and data can be latched out (so that the

host processor can use polling techniques).

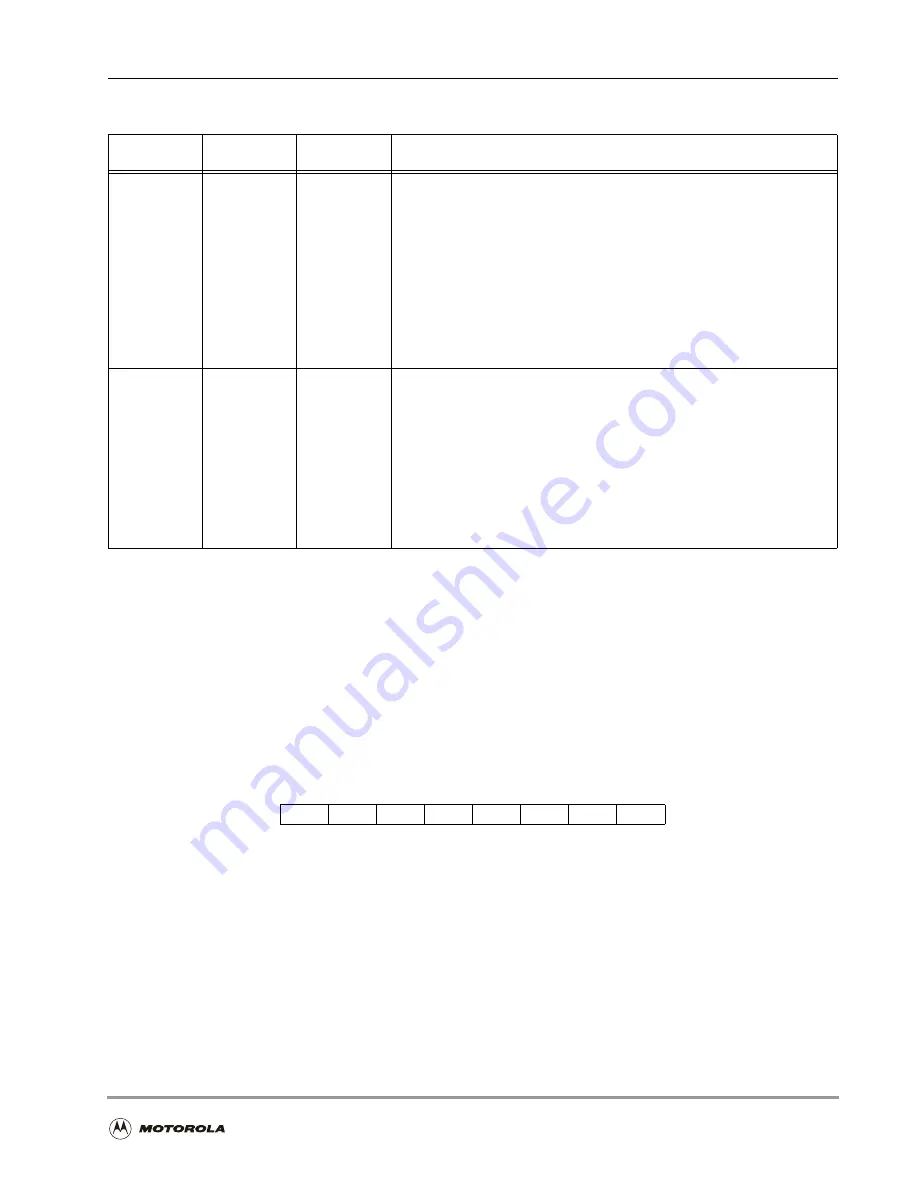

7

6

5

4

3

2

1

0

IV7

IV6

IV5

IV4

IV3

IV2

IV1

IV0

Figure 6-18. Interrupt Vector Register (IVR)

Table 6-17. Interface Status Register (ISR) Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description

Summary of Contents for DSP56303

Page 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Page 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Page 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Page 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Page 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Page 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Page 320: ...Index 14 DSP56303 User s Manual ...