ESSI Programming Model

Enhanced Synchronous Serial Interface (ESSI)

7

-17

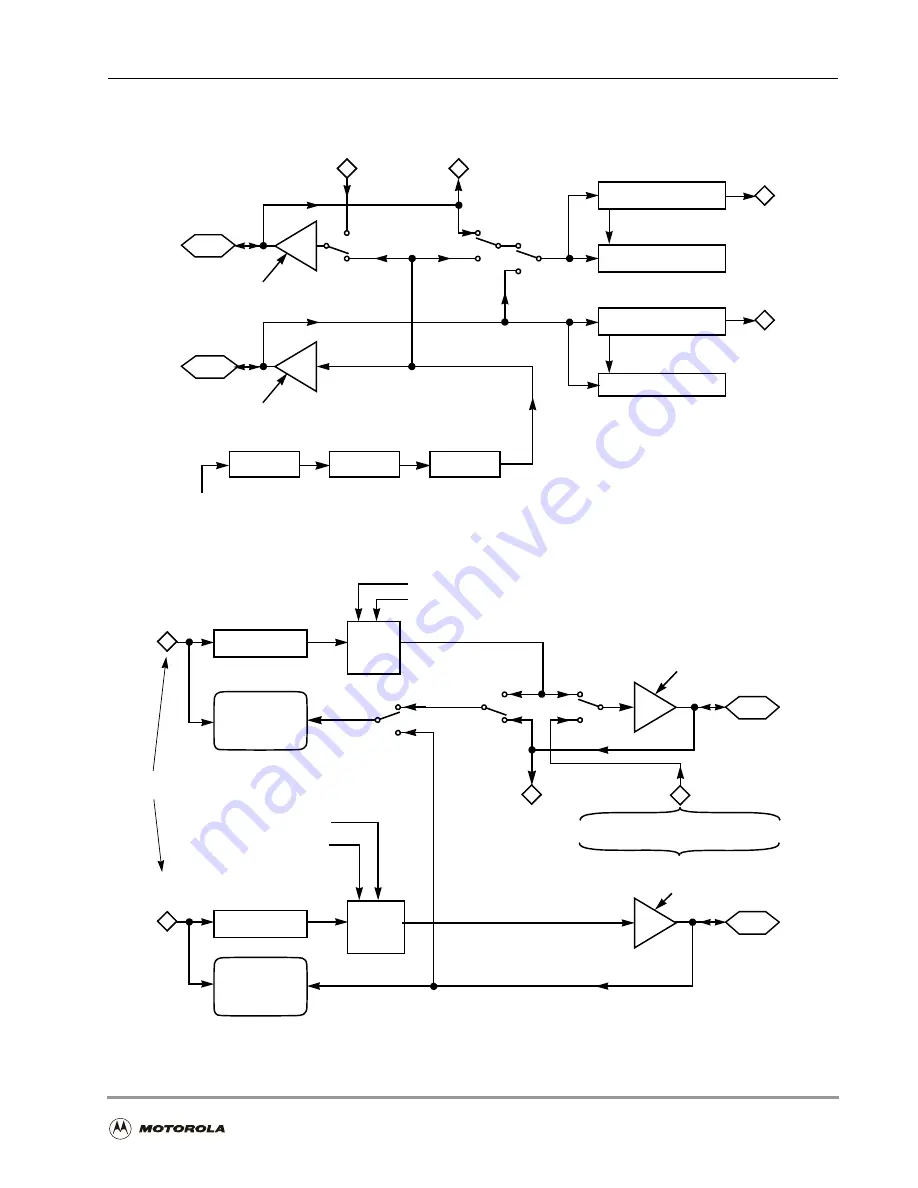

Figure 7-3. ESSI Clock Generator Functional Block Diagram

Figure 7-4. ESSI Frame Sync Generator Functional Block Diagram

SCn0

SCKn

CRB(SCD0)

CRB(SCKD)

CRB(SYN) =

SCD0 = 0

RCLOCK

TCLOCK

Internal Bit Clock

SYN = 1

CRA(WL2–0)

RX Shift Register

TX Shift Register

/1 or /8

/1 to /256

F

CORE

RX

Word

Clock

SYN = 0

SCD0 = 1

Note:1. F

CORE

is the DSP56300 core

internal clock frequency.

2. ESSI internal clock range:

min = F

OSC

/4096

max = F

OSC

/4

3. ‘n’ in signal name is ESSI # (0 or 1)

Sync:

TX 1, or

Async:

RX clk

Sync:

TX/RX clk

Async:

TX clk

0

0

0

255

CRA(PSR)

CRA(PM7:0)

/8, /12, /16, /24,

1

2

3 4,5

Flag0 Out

(Sync Mode)

CRB(OF0)

CRB(TE1)

TX 1

Flag0 In

(Sync Mode)

SSISR(IF0)

1

SYN = 0

0

/8, /12, /16, /24,

1

2

3 4,5

/2

CRA(WL2–0)

TX

Word

Clock

Flag0

(Opposite

from SSI)

or

Frame Sync

Transmit

Frame Sync

Receive

RX Word

Clock

TX Word

Clock

CRA(DC4:0)

Receive

Control

Logic

Transmit

Control

Logic

Sync-

Type

Sync

Type

CRB(SYN) = 0

SYN =

Internal Rx Frame Sync

CRB(SCD1) = 1

SYN = 1

SCD1 =

SYN = 0

CRB(SCD1)

Internal TX Frame Sync

SCn1

/1 to /32

31

0

CRB(FSL1)

CRB(FSL[1–0])

CRA(DC4–0)

/1 to /32

31

0

SCn2

CRB(SCD2)

Flag1 Out,

(Sync Mode)

CRB(OF1)

CRB(TE2)

TX 2,

or drive enb.

CRA(SSC1)

Flag1 In

SSISR(IF1)

(Sync Mode)

CRB(FSR)

Sync:

TX 2 Flag1,

Async:

RX F.S.

or drive enb.

Sync:

TX/RX F.S.

Async:

TX F.S.

CRB(FSR)

These signals are

identical in sync mode.

Summary of Contents for DSP56303

Page 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Page 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Page 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Page 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Page 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Page 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Page 320: ...Index 14 DSP56303 User s Manual ...