ESSI Programming Model

7

-24

DSP56303 User’s Manual

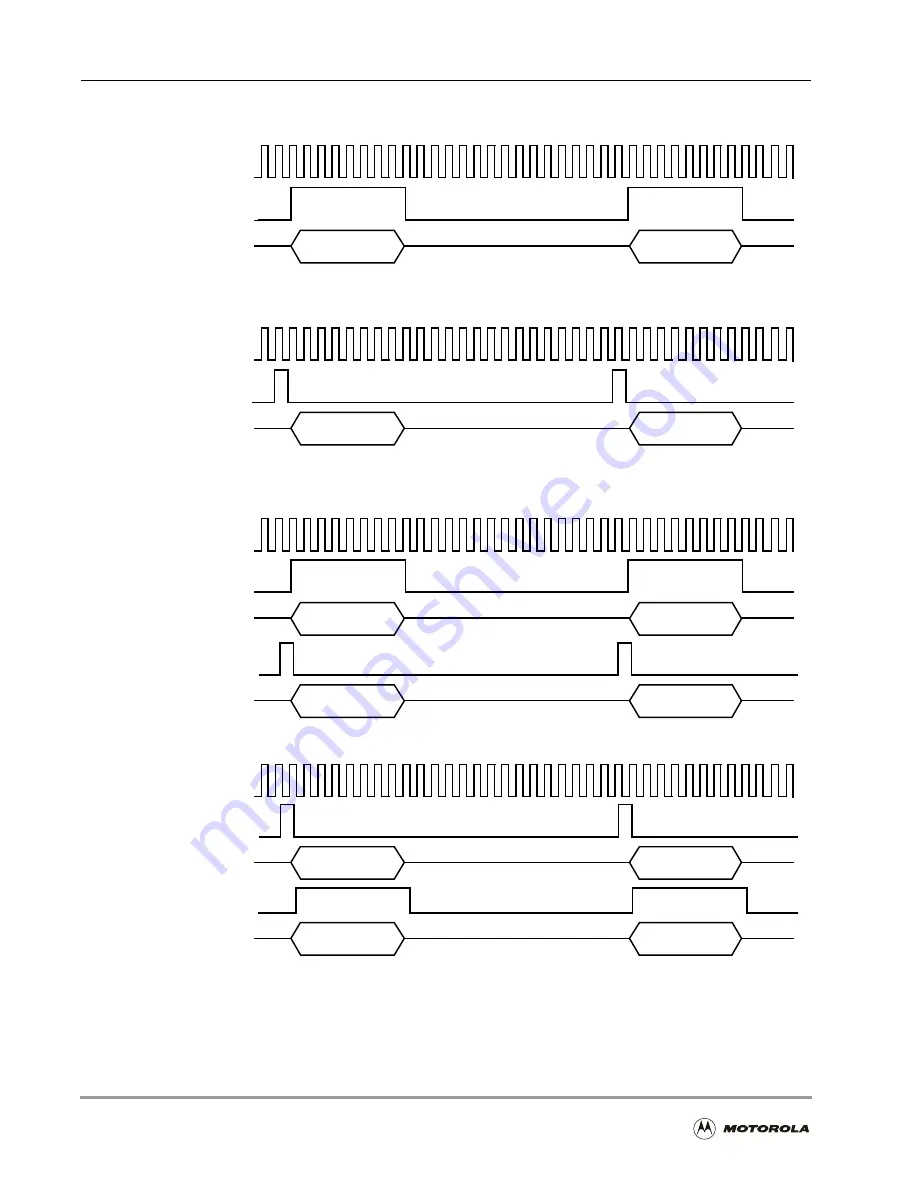

Figure 7-6. CRB FSL0 and FSL1 Bit Operation (FSR = 0)

Serial Clock

RX, TX Frame SYNC

Word Length: FSL1 = 0, FSL0 = 0

RX, TX Serial Data

NOTE: Frame sync occurs while data is valid.

Data

Data

Serial Clock

RX, TX Frame SYNC

One Bit Length: FSL1 = 1, FSL0 = 0

RX, TX Serial Data

NOTE: Frame sync occurs for one bit time preceding the data.

Serial Clock

TX Frame SYNC

Mixed Frame Length: FSL1 = 0, FSL0 = 1

RX Frame Sync

Serial Clock

TX Frame SYNC

Mixed Frame Length: FSL1 = 1, FSL0 = 1

TX Serial Data

RX Frame SYNC

Data

Data

Data

Data

Data

Data

Data

Data

Data

Data

RXSerial Data

TX Serial Data

RX Serial Data

Summary of Contents for DSP56303

Page 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Page 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Page 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Page 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Page 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Page 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Page 320: ...Index 14 DSP56303 User s Manual ...