GPIO Signals and Registers

7

-38

DSP56303 User’s Manual

7.6.3

Port Data Registers (PDRC and PDRD)

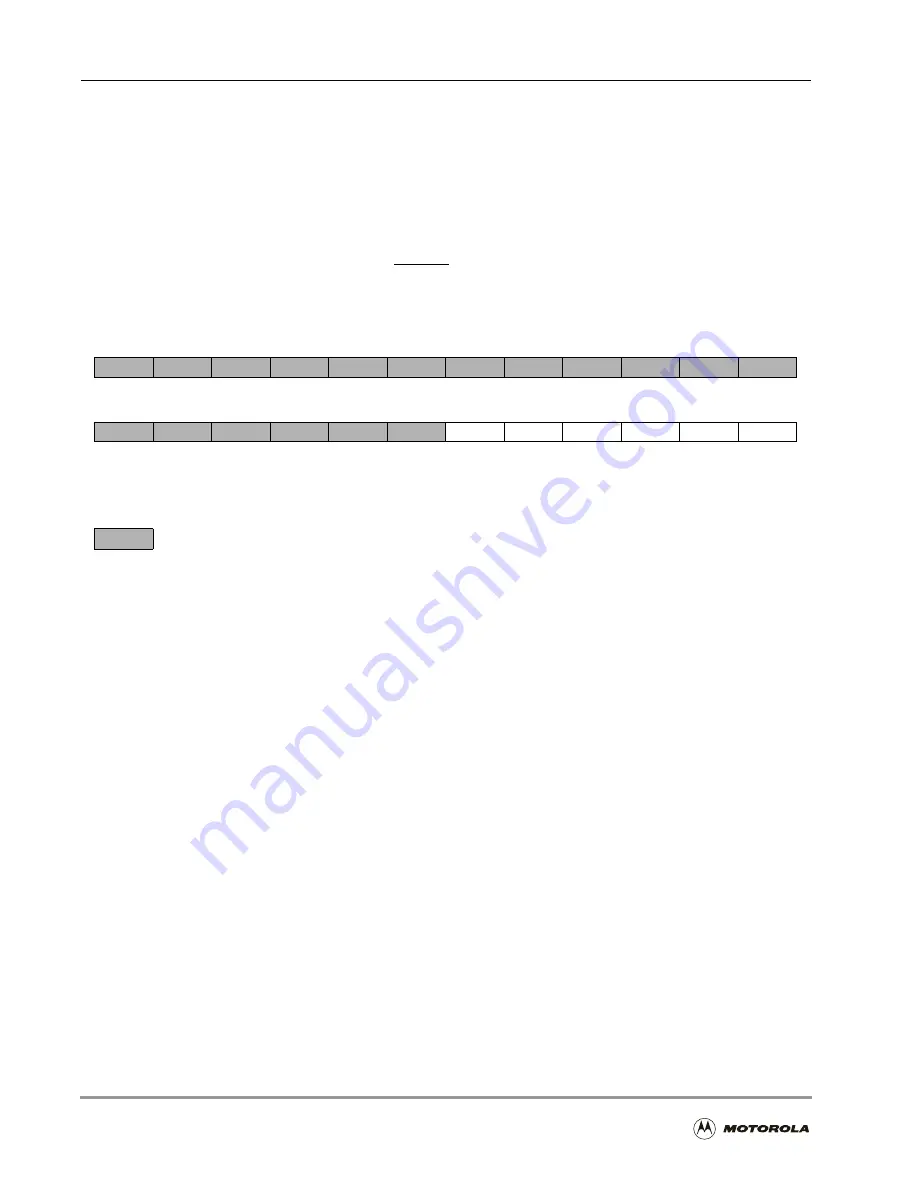

Bits 5–0 of the read/write PDRs write data to or read data from the associated ESSI GPIO

signal lines if they are configured as GPIO signals. If a port signal PC[i] or PD[i] is

configured as an input (GPI), the corresponding PDRC[i] pr PDRD[i] bit reflects the value

present on the input signal line. If a port signal PC[i] or PD[i] is configured as an output

(GPO), a value written to the corresponding PDRC[i] pr PDRD[i] bit is reflected as a value on

the output signal line. Either a hardware

RESET

signal or a software RESET instruction clears

all PDRC and PDRD bits.

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

PDRx5

PDRx4

PDRx3

PDRx2

PDRx1

PDRx0

Note:

For bits 5–0, the value represents the level that is written to or read from the associated signal line if it is

enabled as a GPIO signal by the respective port control register (PCRC or PCRD) bits. For ESSI0, the GPIO

signals are PC[5–0]. For ESSI1, the GPIO signals are PD[5–0]. The corresponding data bits for Port C

GPIOs are PDRC[5–0]. The corresponding data bits for Port D GPIOs are PDRD[5–0].

= Reserved. Read as zero. Write with zero for future compatibility.

Figure 7-20. Port Data Registers (PDRC X:$FFFFBD) (PDRD X: $FFFFAD)

Summary of Contents for DSP56303

Page 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Page 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Page 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Page 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Page 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Page 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Page 320: ...Index 14 DSP56303 User s Manual ...