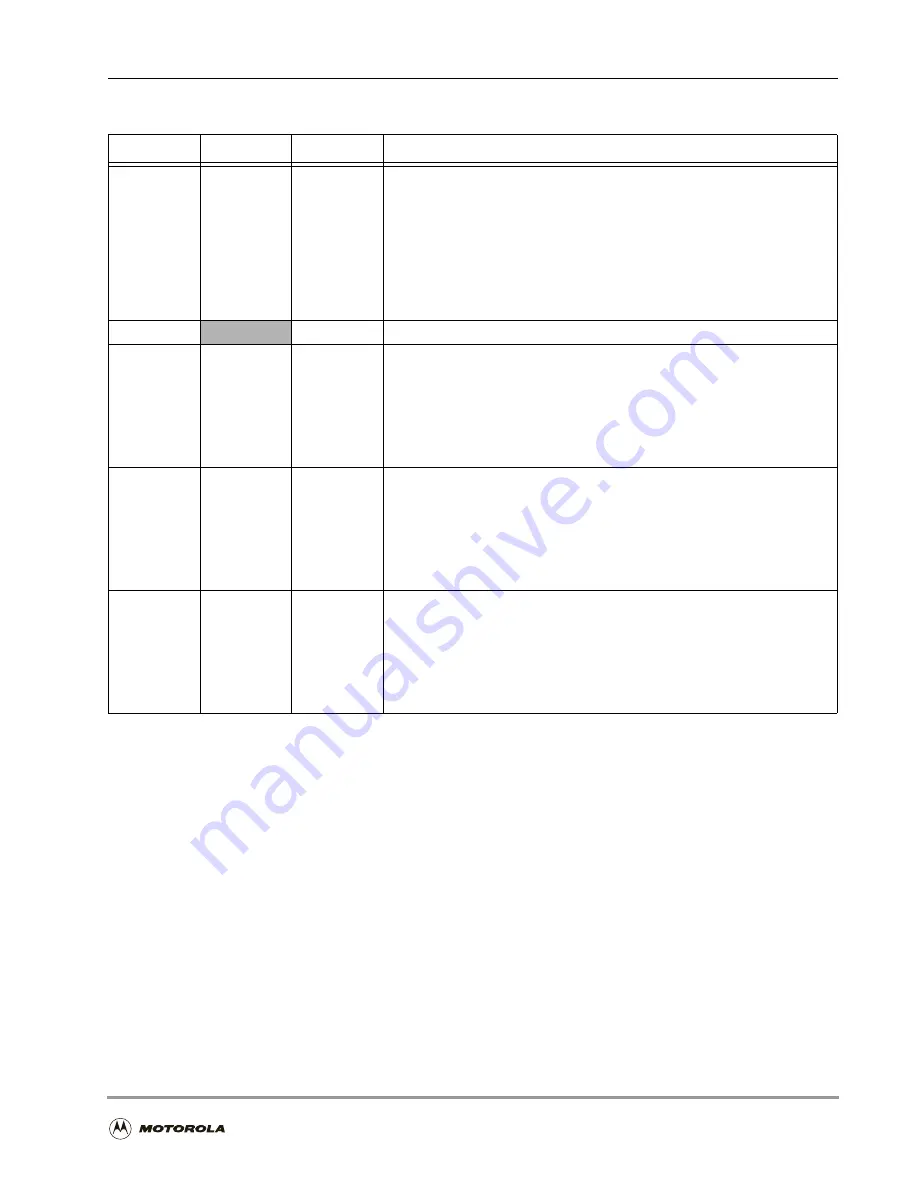

Central Processor Unit (CPU) Registers

Core Configuration

4

-11

19

CE

0

Cache Enable

Enables/disables the instruction cache controller. If CE is set, the cache is

enabled, and instructions are cached into and fetched from the internal

Program RAM. If CE is cleared, the cache is disabled and the DSP56300

core fetches instructions from external or internal program memory,

according to the memory space table of the specific DSP56300 core-based

device.

NOTE: To ensure proper operation, do not clear Cache Enable mode while

Burst mode is enabled (OMR[BE] is set).

18

0

Reserved. Write to zero for future compatibility.

17

SA

0

Sixteen-Bit Arithmetic Mode

Affects data width functionality, enabling the Sixteen-bit Arithmetic mode of

operation. When SA is set, the core uses 16-bit operations instead of 24-bit

operations. In this mode, 16-bit data is right-aligned in the 24-bit memory

locations, registers, and 24-bit register portions. Shifting, limiting, rounding,

arithmetic instructions, and moves are performed accordingly. For details

on Sixteen-Bit Arithmetic mode, consult the

DSP56300 Family Manual.

16

FV

0

DO FOREVER Flag

Set when a DO FOREVER loop executes. The FV flag, like the LF flag, is

restored from the stack when a DO FOREVER loop terminates. Stacking

and restoring the FV flag when initiating and exiting a DO FOREVER loop,

respectively, allow program loops to be nested. When returning from the

long interrupt with an RTI instruction, the system stack is pulled and the

value of the FV bit is restored.

15

LF

0

Do Loop Flag

When a program loop is in progress, enables the detection of the end of the

loop. The LF is restored from stack when a program loop terminates.

Stacking and restoring the LF when initiating and exiting a program loop,

respectively, allow program loops to be nested. When returning from the

long interrupt with an RTI instruction, the System Stack is pulled and the LF

bit value is restored.

Table 4-2. Status Register Bit Definitions (Continued)

Bit Number

Bit Name

Reset Value

Description

Summary of Contents for DSP56303

Page 1: ...DSP56303 User s Manual 24 Bit Digital Signal Processor DSP56303UM AD Revision 1 January 2001 ...

Page 52: ...JTAG OnCE Interface 2 22 DSP56303 User s Manual ...

Page 114: ...General Purpose Input Output GPIO 5 10 DSP56303 User s Manual ...

Page 212: ...GPIO Signals and Registers 8 26 DSP56303 User s Manual ...

Page 268: ...Interrupt Equates A 22 DSP56303 User s Manual ...

Page 306: ...Programming Sheets B 38 DSP56303 User s Manual ...

Page 320: ...Index 14 DSP56303 User s Manual ...