CYCLIC CODE CO-PROCESSOR

CCOP Programming Model

MOTOROLA

DSP56305 User’s Manual

14-19

data words previously generated and transferred to the output FIFO. CIDN can also be

cleared by reading CFSRA- this is used when CCOP processing is terminated without

entering the output phase (e.g. Output Counter = 0). CIDN is cleared by hardware,

software, or CCOP individual reset.

14.4.4.15

Parity Coding Done bit (PCDN)—CCSR Bit 23

The read-only status bit Parity Coding Done (PCDN), when set, indicates that Parity

Coding processing on the input data block is terminated. PCDN is enabled when CCOP

operates in the Parity Coding modes (OPM1 = 1) and is disabled otherwise. PCDN is set

when the CCOP has completed all phases of the processing (i.e., the Input and Run

phases). If HOZD is set, Parity Coding processing terminates either when the Run

Counter reaches zero or when a zero was detected by the Zero Detect function, and then

PREN is cleared and PCDN is set. These conditions allow easy implementation of cyclic

Fire decoders for burst error detection and correction. As a result, the contents of the

Run Counter can be used to calculate the location of the erroneous burst in the data

block, and the contents of CFSRs (CFSRA and CFSRB) can be used to determine the burst

correction sequence. If PCDN and PDIE are set, a Parity Coding Done interrupt vector is

generated. PCDN is cleared when CFSRA is read by the DSP56300 core. PCDN is cleared

by hardware, software. or CCOP individual reset.

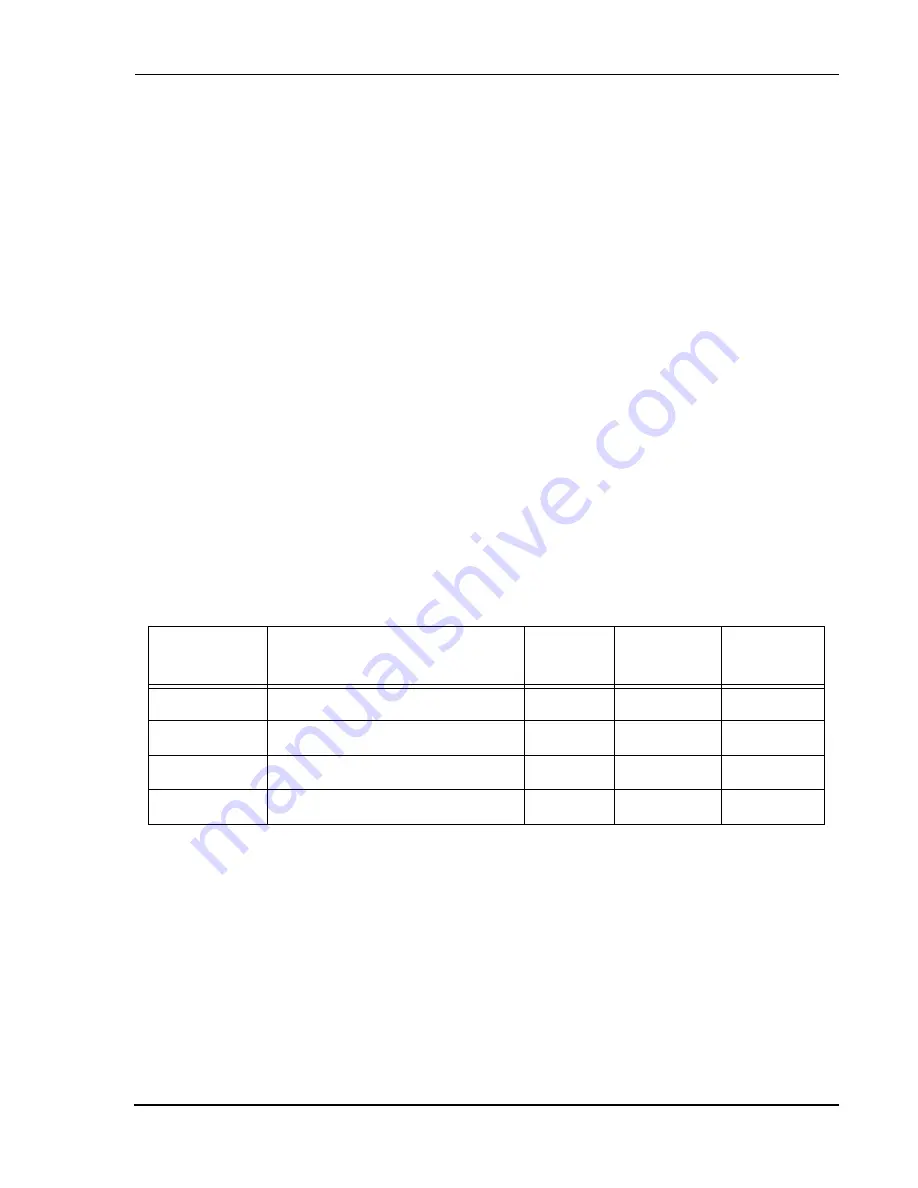

Interrupt options are summarized in Table .

14.4.5

Cyclic Code Processing Registers

These registers are grouped into four identical sets, so this discussion refers to them

generically (for instance as CFSR) instead of individually (for instance as CFSRA,

CFSRB, CFSRC, or CFSRD). In programming these registers, it is necessary to specify

which of the register sets are being programmed (A, B, C, or D).

Table 14-6

CCOP Interrupt Vectors

Interrupt

Address

Interrupt

Vector

Interrupt

Enable

Interrupt

Conditions

DMA

Capability

VBA+Base+0

Input FIFO Empty

DIIE

INFE = 1

Yes

VBA+Base+2

Output FIFO Not Empty

DOIE

OFNE = 1

No

VBA+Base+4

Cipher Processing Done

CDIE

CIDN = 1

Yes

VBA+Base+6

Parity Coding Processing Done

PDIE

PCDN = 1

No

Summary of Contents for DSP56305

Page 34: ...xxxii DSP56305 User s Manual MOTOROLA ...

Page 40: ...xxxvi DSP56305 User s Manual MOTOROLA ...

Page 41: ...MOTOROLA DSP56305 User s Manual 1 1 SECTION 1 DSP56305 OVERVIEW ...

Page 58: ...1 18 DSP56305 User s Manual MOTOROLA DSP56305 Overview DSP56305 Architecture Overview ...

Page 59: ...MOTOROLA DSP56305 User s Manual 2 1 SECTION 2 SIGNAL CONNECTION DESCRIPTIONS ...

Page 98: ...2 40 DSP56305 User s Manual MOTOROLA Signal Connection Descriptions JTAG OnCE Interface ...

Page 99: ...MOTOROLA DSP56305 User s Manual 3 1 SECTION 3 MEMORY CONFIGURATION ...

Page 119: ...MOTOROLA DSP56305 User s Manual 4 1 SECTION 4 CORE CONFIGURATION ...

Page 144: ...4 26 DSP56305 User s Manual MOTOROLA Core Configuration JTAG Boundary Scan Register BSR ...

Page 145: ...MOTOROLA DSP56305 User s Manual 5 1 SECTION 5 GENERAL PURPOSE I O ...

Page 149: ...HOST INTERFACE HI32 MOTOROLA DSP56305 User s Manual 6 1 SECTION 6 HOST INTERFACE HI32 ...

Page 150: ...6 2 DSP56305 User s Manual MOTOROLA HOST INTERFACE HI32 ...

Page 259: ...MOTOROLA DSP56305 User s Manual 7 1 SECTION 7 ENHANCED SYNCHRONOUS SERIAL INTERFACE ESSI ...

Page 315: ...MOTOROLA DSP56305 User s Manual 8 1 SECTION 8 SERIAL COMMUNICATION INTERFACE SCI ...

Page 347: ...MOTOROLA DSP56305 User s Manual 9 1 SECTION 9 TIMER EVENT COUNTER ...

Page 376: ...9 30 DSP56305 User s Manual MOTOROLA Timer Event Counter Timer Modes of Operation ...

Page 377: ...MOTOROLA DSP56305 User s Manual 10 1 SECTION 10 ON CHIP EMULATION MODULE ...

Page 411: ...MOTOROLA DSP56305 User s Manual 11 1 SECTION 11 JTAG PORT ...

Page 430: ...11 20 DSP56305 User s Manual MOTOROLA JTAG Port DSP56305 Boundary Scan Register ...

Page 431: ...Filter Co Processor MOTOROLA DSP56305 User s Manual 12 1 SECTION 12 FILTER CO PROCESSOR ...

Page 471: ...VITERBI CO PROCESSOR MOTOROLA DSP56305 User s Manual 13 1 SECTION 13 VITERBI CO PROCESSOR ...

Page 522: ...13 52 DSP56305 User s Manual MOTOROLA VITERBI CO PROCESSOR References ...

Page 554: ...14 32 DSP56305 User s Manual MOTOROLA CYCLIC CODE CO PROCESSOR Configuration Examples ...

Page 555: ...MOTOROLA DSP56305 User s Manual A 1 APPENDIX A BOOTSTRAP CODE ...

Page 568: ...A 14 DSP56305 User s Manual MOTOROLA Bootstrap Code ...

Page 569: ...Equates MOTOROLA DSP56305 User s Manual B 1 APPENDIX B EQUATES ...

Page 589: ...MOTOROLA DSP56305 User s Manual C 1 APPENDIX C JTAG BSDL ...

Page 590: ...C 2 DSP56305 User s Manual MOTOROLA JTAG BSDL ...

Page 600: ...C 12 DSP56305 User s Manual MOTOROLA JTAG BSDL ...

Page 601: ...MOTOROLA DSP56305 User s Manual D 1 APPENDIX D PROGRAMMING REFERENCE ...

Page 602: ...D 2 DSP56305 User s Manual MOTOROLA PROGRAMMING REFERENCE ...

Page 661: ...Y MOTOROLA DSP56305 User s Manual Index 11 ...

Page 662: ...Y Index 12 DSP56305 User s Manual MOTOROLA ...