On-Chip Emulation Module

OnCE Memory Breakpoint Logic

MOTOROLA

DSP56309UM/D 10-9

10.4.3.5

Trace Occurrence (TO) Bit 4

The TO bit is a read-only status bit that is set when debug mode is entered when the

trace counter is zero while trace mode is enabled. This bit is cleared when leaving debug

mode.

10.4.3.6

Reserved OCSR Bit 5

Bit 5 is reserved for future use. It is read as 0 and should be written with 0 for future

compatibility.

10.4.3.7

Core Status (OS0, OS1) Bits 6-7

The OS0, OS1 bits are read-only status bits that provide core status information. By

examining the status bits, the user can determine whether the chip has entered debug

mode. Examining SWO, MBO, and TO identifies the cause of entering debug mode. The

user can also examine these bits and determine the cause why the chip has not entered

debug mode after debug event (DE) assertion or as a result of the execution of the JTAG

debug request instruction (core waiting for the bus, STOP or WAIT instruction, etc.).

These bits are also reflected in the JTAG instruction shift register, which allows the

polling of the core status information at the JTAG level. This is useful when the

DSP56300 core executes the STOP instruction (and therefore there are no clocks) to allow

the reading of OSCR. See

for the definition of the OS0ÐOS1 bits.

10.4.3.8

Reserved Bits 8-23

Bits 8Ð23 are reserved for future use. They are read as 0 and should be written with 0 for

future compatibility.

10.5

OnCE MEMORY BREAKPOINT LOGIC

Memory breakpoints can be set on program memory or data memory locations. In

addition, the breakpoint does not have to be in a specific memory address, but within an

approximate address range where the program may be executing. This significantly

increases the programmerÕs ability to monitor what the program is doing in real time.

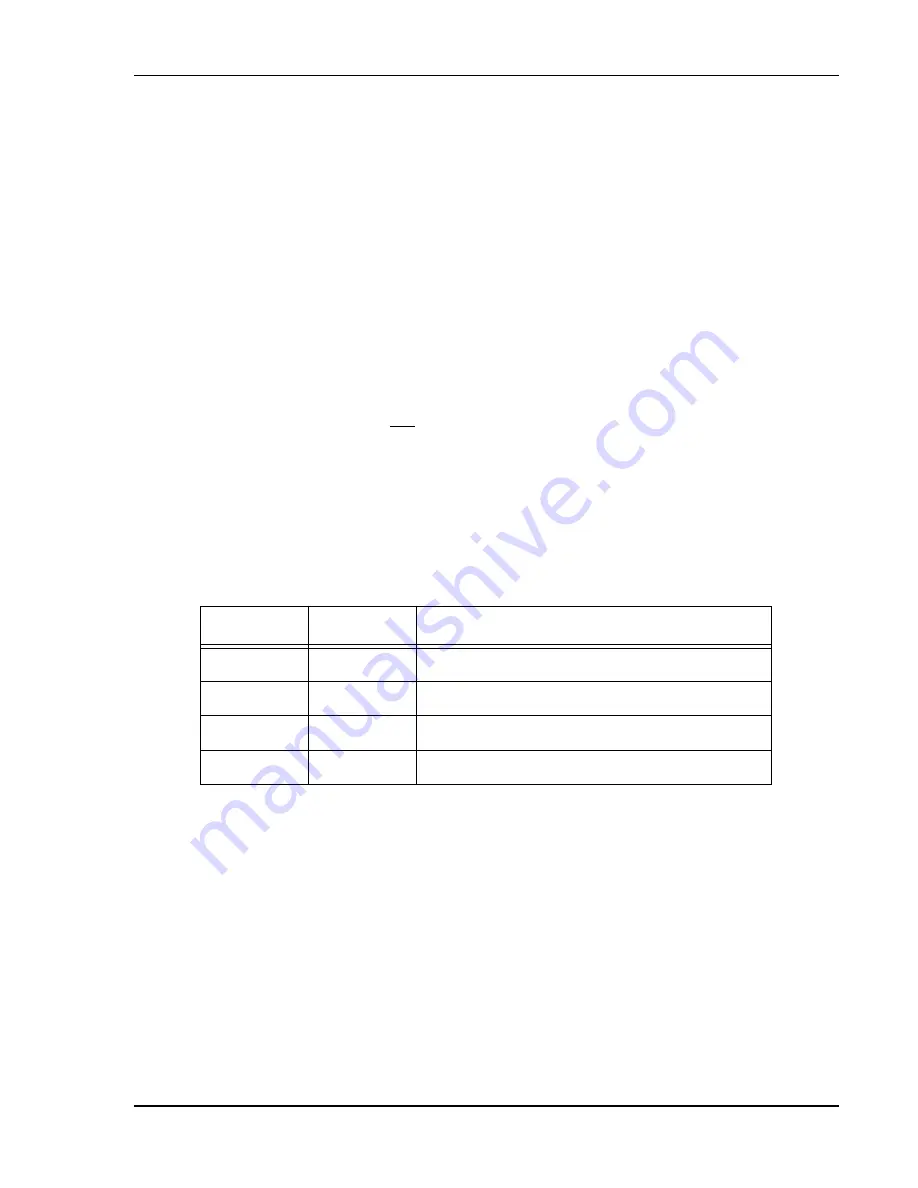

Table 10-5

Core Status Bits Description

OS1

OS0

Description

0

0

DSP56300 core is executing instructions

0

1

DSP56300 core is in wait or stop

1

0

DSP56300 core is waiting for bus

1

1

DSP56300 core is in debug mode

Summary of Contents for DSP56309

Page 25: ...xxii DSP56309UM D MOTOROLA Figure D 25 Port E Registers PCRE PRRE PDRE D 39 ...

Page 30: ...MOTOROLA DSP56309UM D 1 1 SECTION 1 DSP56309 OVERVIEW ...

Page 47: ...1 18 DSP56309UM D MOTOROLA DSP56309 Overview DSP56309 Architecture Overview ...

Page 48: ...MOTOROLA DSP56309UM D 2 1 SECTION 2 SIGNAL CONNECTION DESCRIPTIONS ...

Page 85: ...2 38 DSP56309UM D MOTOROLA Signal Connection Descriptions OnCE JTAG Interface ...

Page 86: ...MOTOROLA DSP56309UM D 3 1 SECTION 3 MEMORY CONFIGURATION ...

Page 104: ...MOTOROLA DSP56309UM D 4 1 SECTION 4 CORE CONFIGURATION ...

Page 124: ...MOTOROLA DSP56309UM D 5 1 SECTION 5 GENERAL PURPOSE I O ...

Page 125: ...5 2 DSP56309UM D MOTOROLA General Purpose I O 5 1 INTRODUCTION 5 3 5 2 PROGRAMMING MODEL 5 3 ...

Page 128: ...MOTOROLA DSP56309UM D 6 1 SECTION 6 HOST INTERFACE HI08 ...

Page 166: ...MOTOROLA DSP56309UM D 7 1 SECTION 7 ENHANCED SYNCHRONOUS SERIAL INTERFACE ESSI ...

Page 212: ...MOTOROLA DSP56309UM D 8 1 SECTION 8 SERIAL COMMUNICATION INTERFACE SCI ...

Page 241: ...8 30 DSP56309UM D MOTOROLA Serial Communication Interface SCI GPIO Signals and Registers ...

Page 242: ...MOTOROLA DSP56309UM D 9 1 SECTION 9 TRIPLE TIMER MODULE ...

Page 269: ...9 28 DSP56309UM D MOTOROLA Triple Timer Module Timer Operational Modes ...

Page 270: ...MOTOROLA DSP56309UM D 10 1 SECTION 10 ON CHIP EMULATION MODULE ...

Page 302: ...MOTOROLA DSP56309UM D 11 1 SECTION 11 JTAG PORT ...

Page 369: ...C 22 DSP56309UM D MOTOROLA DSP56309 BSDL Listing ...

Page 370: ...MOTOROLA DSP56309UM D D 1 APPENDIX D PROGRAMMING REFERENCE ...

Page 405: ......

Page 409: ......