6-18

DSP56309UM/D MOTOROLA

Host Interface (HI08)

HI08 DSP Side ProgrammerÕs Model

6.5.9

DSP Side Registers After Reset

shows the results of the four reset types on the bits in each of the HI08 registers

accessible by the DSP56309. Reset types are as follows:

¥ Hardware reset (HW)

Ñ

caused by the RESET signal

¥ Software reset (SW)

Ñ

caused by executing the RESET instruction

¥ Individual reset (IR)

Ñ

caused by clearing the HPCR:HEN

¥ Stop reset (ST)

Ñ

caused by executing the STOP instruction.

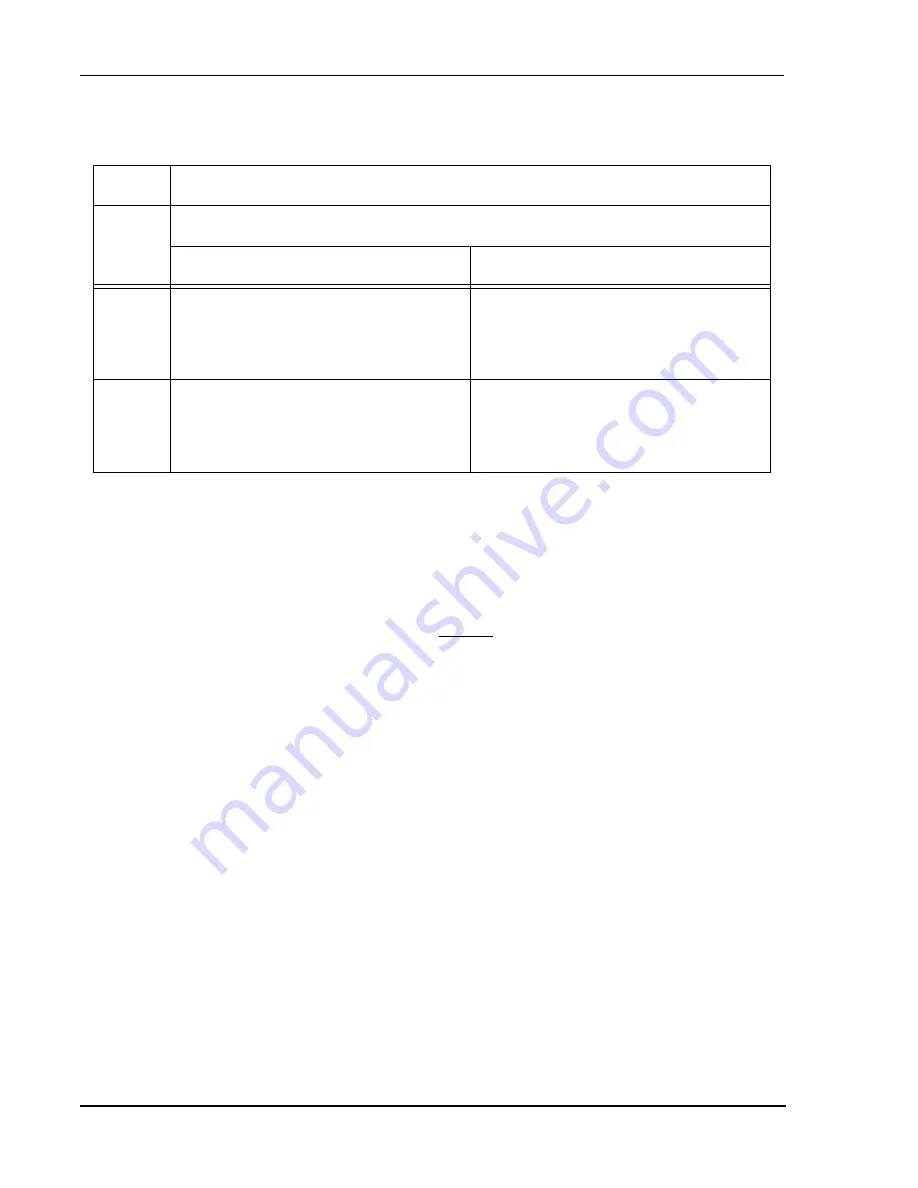

Table 6-5

HDR and HDDR Functionality

HDDR

HDR

DRxx

Dxx

Configured as GPIO signal

Configured as non-GPIO signal

0

Read only bitÑ The value read is the

binary value of the signal. The

corresponding signal is configured as

an input.

Read only bitÑDoes not contain

significant data.

1

Read/write bitÑ The value written is

the value read. The corresponding

signal is configured as an output, and

is driven with the data written to Dxx.

Read/write bitÑ The value written is

the value read.

Summary of Contents for DSP56309

Page 25: ...xxii DSP56309UM D MOTOROLA Figure D 25 Port E Registers PCRE PRRE PDRE D 39 ...

Page 30: ...MOTOROLA DSP56309UM D 1 1 SECTION 1 DSP56309 OVERVIEW ...

Page 47: ...1 18 DSP56309UM D MOTOROLA DSP56309 Overview DSP56309 Architecture Overview ...

Page 48: ...MOTOROLA DSP56309UM D 2 1 SECTION 2 SIGNAL CONNECTION DESCRIPTIONS ...

Page 85: ...2 38 DSP56309UM D MOTOROLA Signal Connection Descriptions OnCE JTAG Interface ...

Page 86: ...MOTOROLA DSP56309UM D 3 1 SECTION 3 MEMORY CONFIGURATION ...

Page 104: ...MOTOROLA DSP56309UM D 4 1 SECTION 4 CORE CONFIGURATION ...

Page 124: ...MOTOROLA DSP56309UM D 5 1 SECTION 5 GENERAL PURPOSE I O ...

Page 125: ...5 2 DSP56309UM D MOTOROLA General Purpose I O 5 1 INTRODUCTION 5 3 5 2 PROGRAMMING MODEL 5 3 ...

Page 128: ...MOTOROLA DSP56309UM D 6 1 SECTION 6 HOST INTERFACE HI08 ...

Page 166: ...MOTOROLA DSP56309UM D 7 1 SECTION 7 ENHANCED SYNCHRONOUS SERIAL INTERFACE ESSI ...

Page 212: ...MOTOROLA DSP56309UM D 8 1 SECTION 8 SERIAL COMMUNICATION INTERFACE SCI ...

Page 241: ...8 30 DSP56309UM D MOTOROLA Serial Communication Interface SCI GPIO Signals and Registers ...

Page 242: ...MOTOROLA DSP56309UM D 9 1 SECTION 9 TRIPLE TIMER MODULE ...

Page 269: ...9 28 DSP56309UM D MOTOROLA Triple Timer Module Timer Operational Modes ...

Page 270: ...MOTOROLA DSP56309UM D 10 1 SECTION 10 ON CHIP EMULATION MODULE ...

Page 302: ...MOTOROLA DSP56309UM D 11 1 SECTION 11 JTAG PORT ...

Page 369: ...C 22 DSP56309UM D MOTOROLA DSP56309 BSDL Listing ...

Page 370: ...MOTOROLA DSP56309UM D D 1 APPENDIX D PROGRAMMING REFERENCE ...

Page 405: ......

Page 409: ......