Core Configuration

Interrupt Priority Registers

MOTOROLA

DSP56367

6-7

6.4

INTERRUPT PRIORITY REGISTERS

There are two interrupt priority registers in the DSP56367:

1. IPR-C is dedicated for DSP56300 Core interrupt sources.

2. IPR-P is dedicated for DSP56367 peripheral interrupt sources.

The interrupt priority registers are shown in Figure 6-1 and Figure 6-2. The Interrupt Priority

Level bits are defined in Table 6-4. The interrupt vectors are shown in Table 6-6 and the

interrupt priorities are shown in Table 6-5.

Mode F

As in Mode C, but HDI08 is set for interfacing to Motorola 68302 bus.

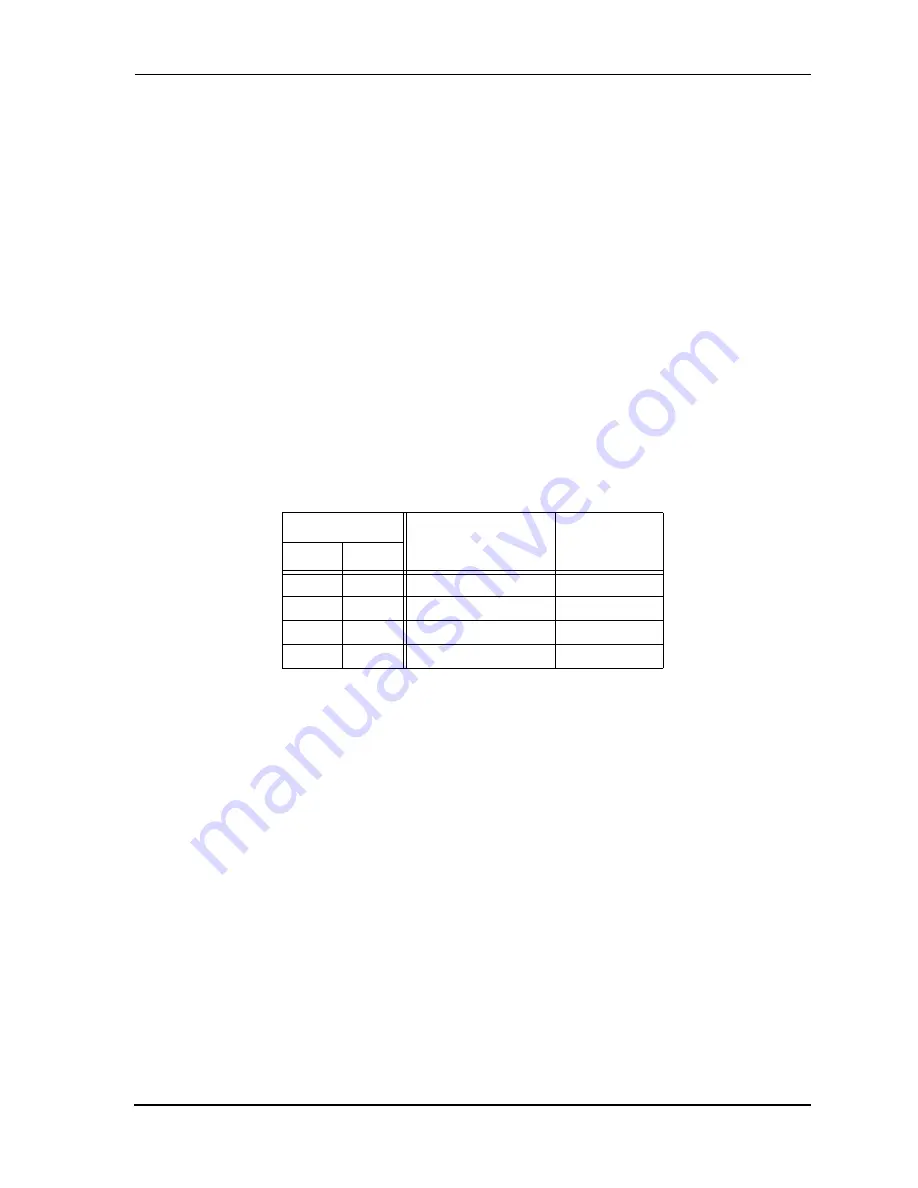

Table 6-4 Interrupt Priority Level Bits

IPL bits

Interrupts

Enabled

Interrupt

Priority

Level

xxL1

xxL0

0

0

No

—

0

1

Yes

0

1

0

Yes

1

1

1

Yes

2

Table 6-3 DSP56367 Mode Descriptions

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......