Host Interface (HDI08)

HDI08 – DSP-Side Programmer’s Model

MOTOROLA

DSP56367

8-7

full HRDF (DSP side) bits are cleared. This transfer operation sets both the TXDE and HRDF

flags. The HORX register contains valid data when the HRDF bit is set. Reading HORX

clears HRDF. The DSP may program the HRIE bit to cause a host receive data interrupt when

HRDF is set. Also, a DMA channel may be programmed to read the HORX when HRDF is

set.

8.5.2

HOST TRANSMIT DATA REGISTER (HOTX)

The 24-bit write-only HOTX register is used for DSP- to-host data transfers. Writing to the

HOTX register clears the host transfer data empty flag HTDE (DSP side). The contents of the

HOTX register are transferred as 24-bit data to the receive byte registers (RXH:RXM:RXL)

when both the HTDE flag (DSP side) and receive data full RXDF flag (host side) are cleared.

This transfer operation sets the RXDF and HTDE flags. The DSP may set the HTIE bit to

cause a host transmit data interrupt when HTDE is set. Also, a DMA Channel may be

programmed to write to HOTX when HTDE is set. To prevent the previous data from being

overwritten, data should not be written to the HOTX until the HTDE flag is set.

Note:

When writing data to a peripheral device, there is a two-cycle pipeline delay until

any status bits affected by the operation are updated. If the programmer reads any

of those status bits within the next two cycles, the bit will not reflect its current

status. See the DSP56300 24-Bit Digital Signal Processor Family Manual,

Motorola publication DSP56300FM/AD for further details.

8.5.3

HOST CONTROL REGISTER (HCR)

The HCR is 16-bit read/write control register used by the DSP core to control the HDI08

operating mode. The initialization values for the HCR bits are described in Section 8.5.9. The

HCR bits are described in the following paragraphs.

8.5.3.1

HCR Host Receive Interrupt Enable (HRIE) Bit 0

The HRIE bit is used to enable the host receive data interrupt request. When the host receive

data full (HRDF) status bit in the host status register (HSR) is set, a host receive data interrupt

request occurs if HRIE is set. If HRIE is cleared, HRDF interrupts are disabled.

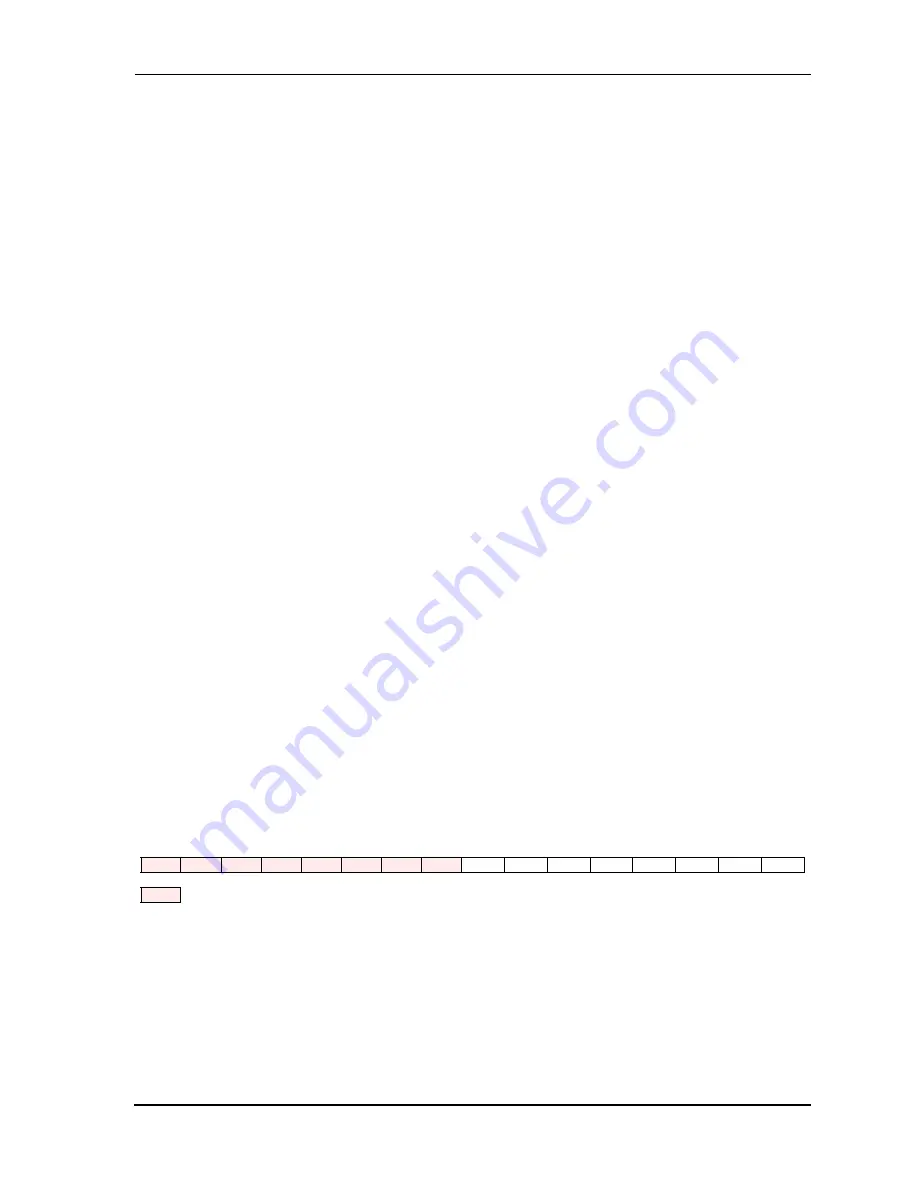

Figure 8-2 Host Control Register (HCR) (X:$FFFFC2)

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

HDM2 HMD1 HDM0

HF3

HF2

HCIE

HTIE

HRIE

- Reserved bit. Read as 0. Should be written with 0 for future compatibility.

Summary of Contents for DSP56367

Page 16: ...xvi MOTOROLA CONTENTS Paragraph Number Title Page Number ...

Page 22: ...xxii MOTOROLA List of Figures Figure Number Title Page Number ...

Page 26: ...xxvi MOTOROLA List of Tables Table Number Title Page Number ...

Page 148: ...4 6 DSP56367 MOTOROLA Design Considerations PLL Performance Issues ...

Page 248: ...9 30 DSP56367 MOTOROLA Serial Host Interface SHI Programming Considerations ...

Page 306: ...10 58 DSP56367 MOTOROLA Enhanced Serial Audio Interface ESAI ESAI Initialization Examples ...

Page 389: ...Bootstrap ROM Contents MOTOROLA DSP56367 A 15 end ...

Page 390: ...A 16 DSP56367 MOTOROLA Bootstrap ROM Contents ...

Page 432: ...C 8 DSP56367 MOTOROLA JTAG BSDL ...

Page 484: ...D 52 DSP56367 MOTOROLA Programmer s Reference ...

Page 490: ...E 6 DSP56367 MOTOROLA Power Consumption Benchmark ...

Page 516: ...F 26 DSP56367 MOTOROLA IBIS Model ...

Page 522: ...Index 6 MOTOROLA Index ...

Page 523: ......